作者@@:蒋修国@@

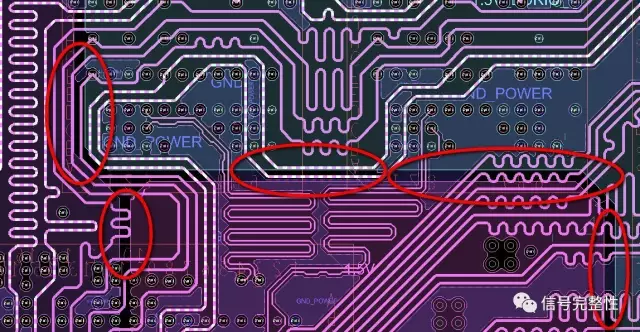

在@@PCB设计过程中经常会遇到高多层@@、高密度的设计@@,那么@@这种情况下就难免出现跨分割@@的情况@@,如下图所示@@:

这是一个@@HDI的项目@@,非常的密集@@,很多点都会出现跨分割@@@@,在@@设计之初@@,针对@@DDR3,经过仿真之后@@,觉得问题不大@@,所以设计工程师和我交流的时候@@@@,告诉他没有问题@@,结果一拿过来@@review的时候@@,傻眼@@。这哪是跨分割@@@@,简直就是分割嘛@@。来回在@@@@gap上@@绕线@@或@@者@@差分线有一根单线直接布在@@@@gap上@@,十有八九会造成问题@@,不是@@SI的问题@@,就有可能造成@@PI的问题@@,或@@者@@EMI的问题@@。

因为跨分割@@本身就会造成阻抗的不连续@@,阻抗不连续就会造成反射@@,反射过大就有可能造成@@辐射或@@者@@干扰@@,进而@@SSN、串扰@@、EMI,等等问题就有可能接踵而至@@。

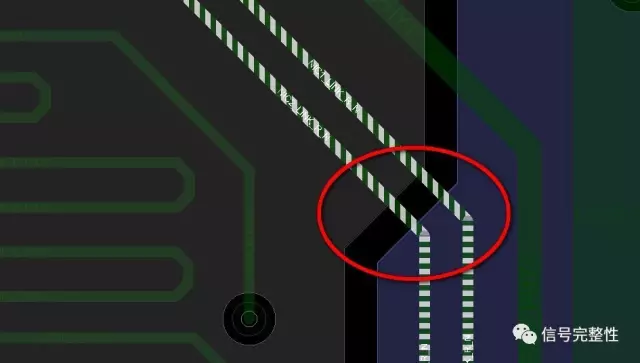

那么@@,如果信号一定要跨分割@@怎么办呢@@?其实这个也没有一个非常好的办法@@,只能说是@@“坏中选优@@”。比如@@:最短的距离跨分割@@@@、不要在@@@@gap上@@绕线@@:

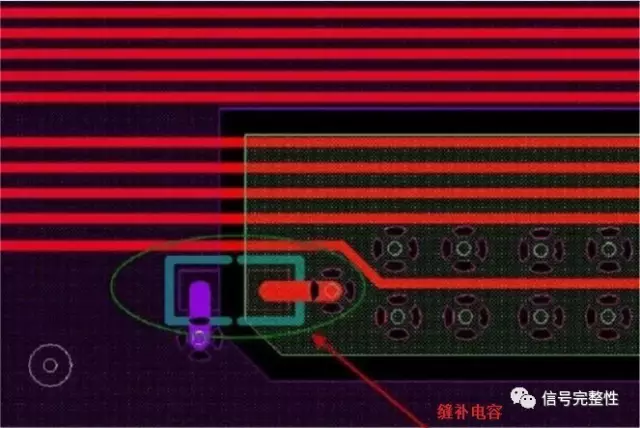

另外@@,缝补电容@@也是常用的一种手段@@,即为跨分割@@的信号提供较短的回流路径@@。通常在@@信号跨分割@@处摆放一个@@ 0201 或@@者@@ 0402大小的瓷片电容@@,电容的容值在@@@@ 0.01uF 或@@者@@是@@ 0.1 uF,这个参数并不是@@一成不变的@@,需要根据信号的频率的变化而改变@@。

当然@@,在@@低速的时候@@@@,在@@EMI的处理方法上@@@@,还可以利用跨接的方式@@,即在@@信号线经过@@gap的区域加一颗@@0ohm的电阻@@。

* 以下方法并不是@@适用于所有设计@@,面对不同的的设计@@,需要工程师自行选择合适的方法进行处理@@。

文章转载自@@: 信号完整性@@微信公众号@@(微信号@@:SI_PI_EMC)