作者@@:蒋修国@@ ,信号完整性@@

在高速电路设计中@@,链路中的每一个参数都有可能导致传递的信号出问题@@。今天就和@@大家分享一个平常大家不太注意的参数@@。

先回顾下在中学的时候@@@@,咱们学习的一个概念@@,趋肤效应@@:当信号的频率较越来越高时@@,信号都会趋向于导体的表面传递@@。这样就会导致信号流过导体的相对有效面积变小@@,从电阻的角度来分析@@,这就会导致电阻增加@@,导致传递能量的损失@@。

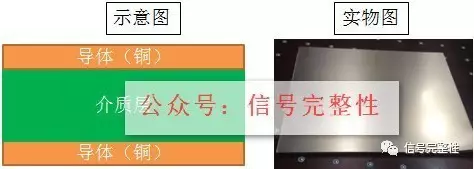

在电子@@产品使用的@@PCB,基本都是由铜@@箔@@和@@有机材料组成的@@,如下图@@所示@@:

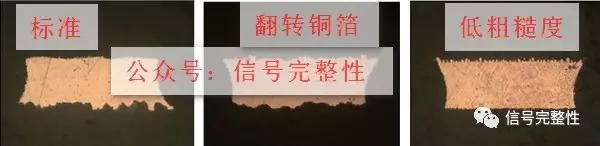

我们平时看到的铜@@箔@@@@,表面上看起来都是非常光滑的@@,实际上并不如你肉眼所见的那样@@,铜@@箔@@并不是完全光滑的@@,其在进项显微镜下如下图@@所示@@@@:

为了更加的容易理解@@,给大家做一个示意图@@@@@@,如下图@@所示@@:

铜@@箔@@的表面都是有很多铜@@牙存在的@@。目前小编没有发现非常官方的数据说明普通的铜@@牙到底有多长@@,据小编看到的普通的铜@@箔@@@@,没有经过处理的铜@@牙@@(铜@@箔@@粗糙度@@)一般都是在@@20~30um左右@@。当然@@,常规的根据铜@@箔@@粗糙度@@的厚度@@@@(系数@@)不同@@,目前有标准铜@@箔@@@@、反转铜@@箔@@@@、低粗糙度铜@@箔@@和@@超低粗糙度铜@@箔@@之分@@。

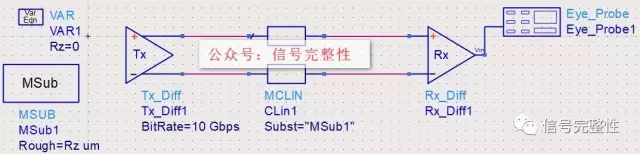

前面说到@@,铜@@箔@@的粗糙度会影响到信号完整性@@@@,那么@@我们就来做一个实验看看@@。原理图@@如下所示@@@@,把铜@@箔@@粗糙度@@的设置为一个变量@@,初始值为@@0,仿真的速率@@为@@10Gbps:

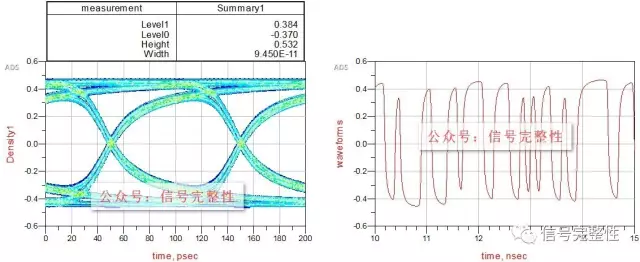

分别查看其眼图@@和@@波形@@@@,如下所示@@:

从结果可以看到@@:眼图@@的宽度为@@97ps,高度为@@0.652V,信号的峰值为@@0.479V。

那么@@,接下来@@,逐步改变铜@@箔@@粗糙度@@的厚度@@@@,观察眼图@@的变化@@,分别仿真铜@@箔@@粗糙度@@为@@5um、10um、15um和@@20um的情况@@,眼图@@和@@波形@@分别如下所示@@@@:

当粗糙度为@@5um的时候@@,眼图@@的宽度为@@94.5ps,高度为@@0.532V。

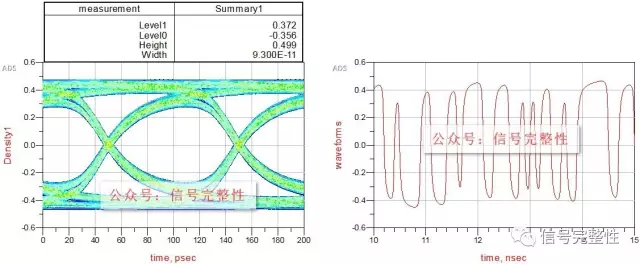

当粗糙度为@@10um的时候@@,眼图@@的宽度为@@93ps,高度为@@0.499V。

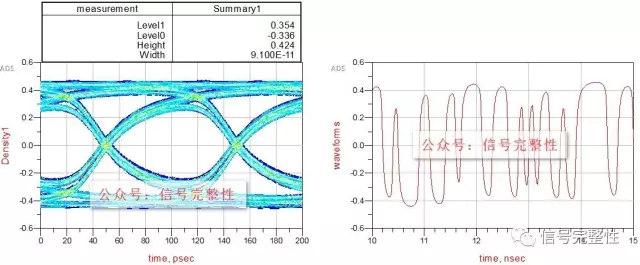

当粗糙度为@@15um的时候@@,眼图@@的宽度为@@91ps,高度为@@0.424V。

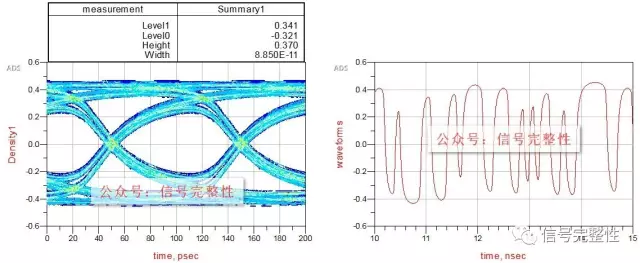

当粗糙度为@@20um的时候@@,眼图@@的宽度为@@88.5ps,高度为@@0.370V。

从以上的结果@@,咱们可以看到当铜@@箔@@粗糙度@@的系数@@@@(厚度@@)增加时@@,眼图@@的的@@margin越来越小@@,抖动@@(Jitter)越来越大@@。

有的工程师经常会问到这样一个问题@@:当信号的速率为多少的时候@@@@,在实际项目工程中需要考虑铜@@箔@@粗糙度@@的影响@@。我的答案是@@,任何时候考虑都是必要的@@。但是综合成本和@@效果来考虑的话@@,当信号速率超过@@5G以上的时候@@@@,就应当适当的考虑铜@@箔@@的选择问题@@(如果设计要求不高@@,也可以不考虑@@)。

所以@@,当信号的速率越来越高的时候@@@@,我们不仅仅需要关注芯片的驱动能力@@、PCB介质的介电常数@@、介质损耗角@@、连接器@@、线缆等等@@,还需要考虑到导体@@(铜@@)的表面粗糙度的影响@@。

文章来源@@:信号完整性@@