在@@大多数电子@@系统中@@@@,降噪是一@@个重要设计问题@@。与@@功耗限制@@、环境温度变化@@、尺寸限制以及速度和@@精度要求一@@样@@,必须处理好无所不在@@的@@噪声因素@@,才能使最终设计获得成功@@。

这里@@,我们不考虑用于降低@@“外部噪声@@”(与@@信号@@一@@起到达系统@@)的@@技术@@@@,因为其存在@@一@@般不受设计工程师直接控制@@。相比之下@@,防止@@“内部噪声@@”(电路或@@系统内部产生或@@耦合的@@噪声@@)扰乱信号@@则是设计工程师的@@直接责任@@。今天我们就说说@@“接地@@@@”,而且是针对@@高频工作的@@@@“接地@@@@"

“接地@@@@”(Grounding)一@@般指将电路@@、设备@@或@@系统连接到一@@个作为参考电位@@点或@@参考电位@@面的@@良好导体上@@@@,为电路或@@系统与@@@@“地@@”之间建立一@@个低阻抗的@@通道@@。

地@@线@@是作为电路或@@系统电位@@基准点的@@等电位@@体@@,是系统中@@各个电路的@@公共导体@@,任何电路的@@电流都会经过地@@线@@形成回路@@。然而@@,任何导体都存在@@着一@@定的@@阻抗@@,当地@@线@@中@@有电流通过时@@@@,根据欧姆定律@@,地@@线@@上@@就会有电压存在@@@@,那么@@地@@线@@就不是一@@个等电位@@体@@。所以在@@实际设计电路或@@系统时@@@@,关于地@@线@@上@@各点的@@电位@@一@@定相等的@@假设就不是成立的@@@@,实际的@@情况是底线上@@各点存在@@电位@@差@@,有的@@相位@@差还可能很大@@。地@@线@@的@@公共阻抗会使各接地@@@@点间形成一@@定的@@电压@@,从而就会产生接地@@@@干扰@@。

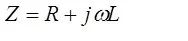

如上@@面所说@@,地@@线@@作为导体@@,存在@@一@@定的@@阻抗@@,顾名思义@@,阻抗也就是由电阻和@@感抗两部分组成@@,即@@:

导体的@@阻抗是频率的@@函数@@,随着频率的@@升高@@,阻抗增加很快@@。对@@于高速数字电路@@而言@@,电路的@@时@@钟频率是很高的@@@@,脉冲信号@@包涵丰富的@@高频成分@@,因此@@会在@@地@@线@@上@@产生较大的@@电压@@,则地@@线@@阻抗@@对@@数字电路的@@干扰@@十分可观@@。

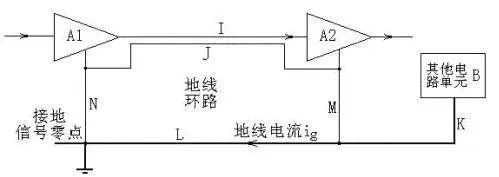

在@@电子@@产品的@@@@PCB设计中@@@@,抑制或@@防止@@地@@线@@干扰是需要考虑的@@最主要问题之一@@@@。所谓干扰@@,必然是发生在@@不同的@@单元电路@@@@、部件或@@系统之间@@,而地@@线@@干扰是指通过公用地@@线@@的@@方式产生的@@信号@@干扰@@。注意@@这里@@所提到的@@信号@@@@,通常是指交流信号@@或@@者跳变信号@@@@。地@@线@@干扰的@@形式很多@@,有人把它归结成两类@@:地@@线@@环路@@干扰@@、公共阻抗干扰@@,其实应该还要加上@@地@@线@@环路@@的@@电磁耦合干扰@@,因此@@是三@@类@@。下图@@可以很好的@@说明三@@类地@@线@@干扰的@@成因@@。

一@@、地@@环路干扰@@。

横向@@,每根导线上@@的@@电流不同@@,因此@@会产生差模电压@@,对@@电路造成影响@@。具体的@@说就是@@“其他电路单元@@B”的@@地@@线@@电流@@,在@@J、N、L、M形成的@@@@“地@@线@@环路@@”中@@,对@@放大器@@A1和@@A2造成了影响@@。由于这种干扰是由电缆与@@地@@线@@构成的@@环路电流产生的@@@@,因此@@成为@@地@@环路干扰@@@@。

二@@、地@@环路电磁耦合干扰@@。

在@@实际电路的@@@@PCB上@@,J、N、L、M形成的@@@@“地@@线@@环路@@”将包围一@@定的@@面积@@,根据电磁感应定律@@,如果这个环路所包围的@@面积中@@有变化的@@磁场存在@@@@,就会在@@环路中@@产生感生电流@@,形成干扰@@。空间@@磁场的@@变化无处不在@@@@,于是包围的@@面积越大干扰就越严重@@。

三@@、公共阻抗干扰@@。

认真考察上@@图@@所示的@@电路结构@@,我们将发现@@,J、N、L、M中@@,有一@@条连接是多余的@@@@,随便去除@@其一@@@@,仍然可以满足各个接地@@@@点的@@连通关系@@,同时@@又可以消除地@@线@@环路@@@@。那么@@,将哪一@@条连线去除@@比较合理呢@@?这时@@就要考虑另一@@类的@@干扰@@问题@@——公共阻抗干扰@@。

①去除@@J:这是最差的@@方案@@。J去除@@后地@@线@@环路@@似乎消失了@@,可是另一@@个更可怕的@@环路又形成了@@(I、N、L、M),其中@@@@I是信号@@线@@,因此@@干扰比原来有线@@J时@@还要严重@@。

②去除@@M:环路消失@@,但是@@我们发现@@,此时@@放大器@@A2的@@地@@线@@电流@@需要流过@@J、N到达接地@@@@零点@@,注意@@N段是@@A1和@@A2共同的@@接地@@@@线@@@@,因此@@A2接地@@@@电流在@@@@N上@@形成的@@@@电压降就加到了@@A1上@@,形成干扰@@。这种因共用一@@段地@@线@@而形成的@@@@干扰称为@@“公共阻抗干扰@@”。

③去除@@L:不仅不能解决@@A2与@@A1之间的@@公共阻抗干扰@@问题@@,还引起了@@“B单元电路@@”与@@A1、A2之间的@@公共阻抗干扰@@问题@@。

④去除@@N:看来这是最后的@@方法@@。其实这样做将使@@M成为@@A1、A2的@@“公用阻抗@@”,同样形成干扰@@@@。还是存在@@问题@@!但是@@,我们注意@@到@@,此法中@@的@@干扰@@是@@A1对@@A2的@@干扰@@,A2是后级@@,工作信号@@强度远大于@@A1,因此@@A1对@@A2的@@干扰@@,很难造成不良后果@@。

最合理的@@走线方案是@@:去除@@N,然后将@@M的@@下端直接连到@@“接地@@@@信号@@零点@@”上@@。

以上@@是关于接地@@@@干扰产生的@@原因@@,下面再介绍的@@几种常见的@@接地@@@@方式@@,结合前面对@@接地@@@@干扰产生原因的@@了解@@,有助于我们在@@实际设计@@PCB板电路时@@@@,正确的@@选择干扰最小的@@接地@@@@方式@@,设计出合理的@@电路或@@系统@@。

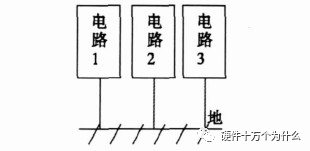

信号@@接地@@@@方式可以大体上@@分为@@:单点接地@@@@@@、多点接地@@@@@@、混合接地@@@@@@和@@悬浮接地@@@@@@@@。

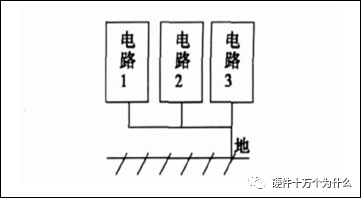

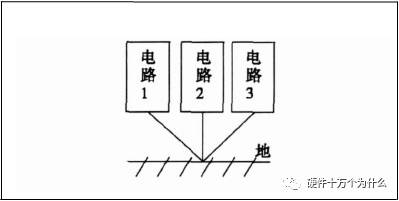

单点接地@@@@@@。单点接地@@@@@@就是把真个电路系统中@@的@@某一@@点作为接地@@@@的@@基准点@@,所有电路及设备@@的@@地@@线@@都必须接到这一@@点上@@@@,并以该点作为电路@@、设备@@的@@零电位@@参考点@@。单点接地@@@@@@又分为串联单点接地@@@@@@@@和@@并联单点接地@@@@@@@@。如下图@@所示@@:

图@@2.串联单点接地@@@@@@@@

对@@于串联式单点接地@@@@@@方式@@,如果该电路的@@功率很大@@,会产生很大的@@电路回流@@,在@@有限阻抗上@@会产生一@@个电压降@@,造成电路和@@基准地@@之间的@@电压参考值的@@差异可能使系统不能如预期的@@那样工作@@。如存在@@多种不同功率等级的@@电路@@,不能采用串联式单点接地@@@@@@方式@@,因为大功率电路产生大的@@回地@@电流@@,将影响低功率器件和@@电路@@。如果说一@@定要采取这种接地@@@@方法@@,那么@@最敏感的@@电路必须直接设置在@@电源输入位@@置处@@,并且尽量远离低功率器件和@@电路@@。串联单点接地@@@@@@@@方式和@@结构都比较简单@@,如果各个电路的@@接地@@@@引线比较短@@,其阻抗也会相对@@小@@。如果各个电路的@@接地@@@@电平差别不大@@,可以采用这种接地@@@@方式@@。

并联单点接地@@@@@@方式中@@@@,每个电路单元独用地@@线@@连接到同意地@@点@@,其优点是各电路的@@地@@点为只与@@本电路的@@地@@电流及地@@线@@阻抗@@有关@@,不受其他电路的@@影响@@。低频时@@可有效的@@避免各电路单元之间的@@低阻抗干扰@@,但是@@也存在@@很多缺点@@。主要表现在@@@@:首先@@,各个电路分别采用独立地@@线@@接地@@@@@@,需要多跟地@@线@@@@,势必增加地@@线@@长度@@,从而增加地@@阻抗@@,结构复杂使用麻烦@@;其次@@,这种接地@@@@方式会造成各地@@线@@互相间的@@耦合@@,并且随着频率增加@@,地@@线@@阻抗@@、地@@线@@电感@@、电线电容都会增大@@,这种接地@@@@方式不适用高频电路@@。

多点接地@@@@@@。多点接地@@@@@@是指某一@@个系统中@@各个需要接地@@@@的@@电路@@、设备@@都直接接到距离它最近的@@接地@@@@平面上@@@@,一@@边接地@@@@长度最短@@,接地@@@@阻抗减到最小@@。

当电子@@系统的@@工作频率高于@@@@1MHz时@@,以致工作波长@@与@@系统接地@@@@引线的@@长度可比拟时@@@@,地@@线@@就象一@@根终端短路的@@传输线@@,地@@线@@的@@电流@@、电压呈驻波分布@@,地@@线@@变成了辐射天线@@,而不能起到地@@线@@的@@作用@@。为了减少接地@@@@阻抗@@,避免辐射@@,地@@线@@的@@长度应小于@@1/20波长@@,因而单点接地@@@@@@方法是不合理的@@@@,通常采用多点接地@@@@@@技术@@@@。多点接地@@@@@@电路结构简单@@,接地@@@@线@@上@@可能出现的@@高频驻波现象显著减少@@,但多点接地@@@@@@可能会导致设备@@内部形成许多接地@@@@环路@@,容易对@@设备@@内部的@@敏感店里产生地@@环路干扰@@@@。

一@@般来说@@,频率在@@@@1MHz以下时@@可采用单点接地@@@@@@方式@@,频率高于@@10MHz时@@可采用多点接地@@@@@@方式@@,而频率在@@@@@@1——10MHz时@@,通常采用混合接地@@@@@@方式@@。

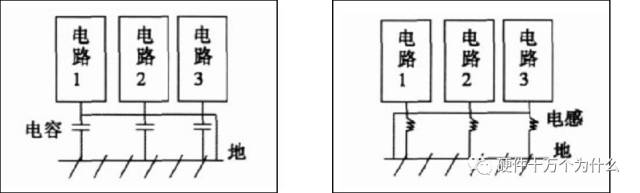

混合接地@@@@@@。混和@@接地@@@@是单点接地@@@@@@和@@多点接地@@@@@@的@@复合@@。在@@PCB 中@@存在@@高低频混合频率时@@@@,常使用这种接地@@@@方式@@。

图@@5.混合接地@@@@@@-容性耦合@@ 图@@6.混合接地@@@@@@-感性耦合@@

图@@5和@@图@@@@6提供了两种混和@@接地@@@@方法@@。对@@于电容耦合型电路@@,在@@低频时@@呈现单点接地@@@@@@结构@@,而在@@高频时@@呈现多点接地@@@@@@状态@@。这是因为电容将高频电流分流到了地@@@@。这种方法成功的@@关键在@@于清楚使用的@@频率和@@接地@@@@电流预期流向@@。在@@接地@@@@拓扑结构中@@使用电容和@@电感@@,使我们能用一@@种优化设计的@@方式控制射频电流@@。通过确定射频电流要通过的@@路径@@@@,可以控制@@PCB 的@@布线@@。对@@射频电流回路缺乏认识可能导致辐射或@@敏感度方面的@@问题@@。

悬浮接地@@@@@@。悬浮地@@是指设备@@的@@地@@线@@系统与@@壳体构件的@@接大地@@系统在@@电气上@@相互绝缘@@,以防止@@壳体构件中@@的@@电磁干扰传导到设备@@中@@去@@。但是@@,由于设备@@不与@@公共地@@相连@@,故悬浮接地@@@@@@容易在@@两者之间造成静电积累@@,当电荷积累到一@@定程度后@@,在@@设备@@与@@公共地@@之间的@@电位@@差可能引起剧烈的@@静电放电@@,产生干扰放电电流@@。悬浮接地@@@@@@不适用于通信系统中@@@@。

了解了以上@@的@@内容@@,那么@@在@@实际的@@@@BCB板的@@印刷中@@@@,要以上@@面的@@理论依据为基础对@@地@@线@@进行合理布局@@。在@@对@@地@@线@@布局时@@@@,通常要注意@@以下几点@@:

一@@、数字地@@与@@模拟地@@要分开@@;

二@@、数字电路地@@线@@不要构成闭合环路@@;

三@@、多层@@PCB中@@,尽量将地@@线@@层和@@电源层放置在@@相邻的@@层中@@@@;

四@@、地@@线@@、电源线和@@信号@@线宽度设计要合理@@。

以上@@这些注意@@点@@,要在@@实际操作中@@慢慢研究体会@@。

在@@进行高速电路设计时@@@@,合理的@@接地@@@@设计是最有效的@@电磁兼容设计技术@@@@。据统计@@,90%的@@电磁兼容问题是由于布线和@@接地@@@@不当造成的@@@@。好的@@布线@@和@@接地@@@@既能够提高@@抗扰度@@,又能减小干扰发射@@,同时@@也有可能再成本较低的@@情况下解决许多电磁干扰问题@@,所以在@@进行高速电路的@@@@PCB板设计时@@@@,合理的@@设计接地@@@@至关重要@@。

一@@般提倡电源和@@信号@@电流最好通过@@“接地@@@@层@@”返回@@,而且该层还可为转换器@@、基准电压源和@@其它子电路提供参考节点@@。但是@@,即@@便广泛使用接地@@@@层@@也不能保证交流电路具有高质量接地@@@@参考@@。

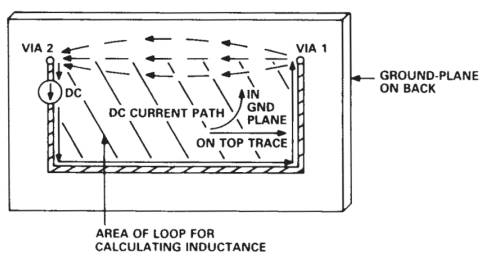

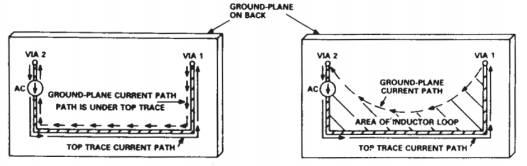

图@@ 1所示为简单电路采用两层印刷电路板制造@@,顶层上@@有一@@个交直流电流源@@,其一@@端连到过孔@@ 1,另一@@端通过一@@条@@ U 形铜走线连到过孔@@ 2。两个过孔均穿过电路板并连到接地@@@@层@@@@。理想情况下@@,阻抗为@@ 0,电流源上@@的@@电压为@@ 0 V。

图@@ 1. 电流源的@@原理图@@和@@布局@@,PC板上@@布设@@U形走线@@,通过接地@@@@层@@返回@@@@。

这个简单的@@原理图@@远不能反映真实的@@情况@@,但了解电流如何在@@接地@@@@层@@中@@从过孔@@ 1 流到过孔@@ 2,将有助于我们看清实际问题所在@@@@,并找到消除高频布局接地@@@@噪声的@@方法@@。

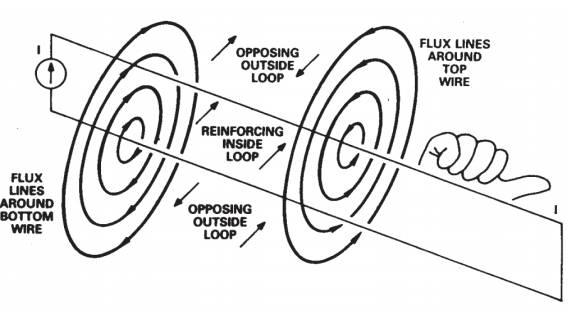

电感与@@电流环路的@@面积成比例@@,二@@者之间的@@关系可以用图@@@@ 2 所示的@@右手法则和@@磁场来说明@@。环路之内@@,沿着环路所有部分流动的@@电流所产生的@@磁场相互增强@@。环路之外@@,不同部分所产生的@@磁场相互削弱@@。因此@@,磁场原则上@@被限制在@@环路以内@@。环路越大则电感越大@@,这意味着@@:对@@于给定的@@电流水平@@,它储存的@@磁能更多@@,阻抗更高@@,因而将在@@给定频率产生更大电压@@。

图@@2. 磁力线和@@感性环路@@

在@@图@@中@@所示的@@简单例子中@@@@,面积最小的@@环路显然是由@@ U 形顶部走线与@@其正下方的@@接地@@@@层@@部分所形成的@@@@环路@@。图@@ 3(左@@)则显示了大多数交流电流在@@接地@@@@层@@中@@选取的@@路径@@@@,它所围成的@@面积最小@@,位@@于@@ U 形顶部导线正下方@@。实际应用中@@@@,接地@@@@层@@电阻会导致低中@@频电流流向直接返回@@路径@@与@@顶部导线正下方之间的@@某处@@(右图@@@@)。不过@@,即@@使频率低至@@ 1-2 MHz,返回@@路径@@也是接近顶部走线的@@下方@@。

图@@ 3. 接地@@@@层@@中@@不含@@(左@@图@@@@)和@@含@@(右图@@@@)电阻的@@交流电流路径@@@@

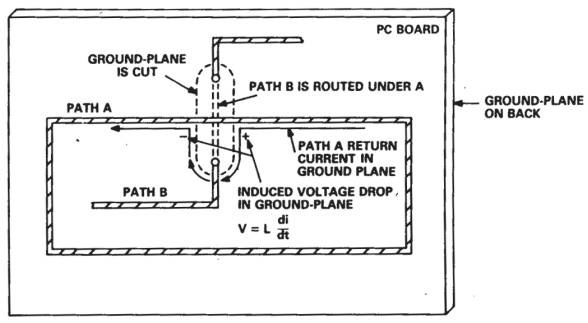

如何避免布局问题@@@@?一@@旦了解电流在@@接地@@@@层@@中@@的@@返回@@路径@@@@,就可以找出并纠正常见布局问题@@@@。例如在@@图@@@@4 中@@,路径@@ A 被认定是关键路径@@@@,应当保持最短@@,远离数字线路@@,并且不得有过孔@@。路径@@ B 不那么@@重要@@,但需要穿过路径@@@@ A。通常是切开路径@@@@ A 下面的@@接地@@@@层@@@@,然后经过两个过孔并在@@路径@@@@ A 下方布设路径@@@@ B。

图@@4. 路径@@交叉时@@的@@典型@@ PCB 布局问题@@

但结果令人遗憾@@,两个信号@@的@@接地@@@@回路中@@均引入了电感@@,因为中@@断的@@接地@@@@层@@使两条环路的@@面积均变得更大@@。路径@@ A 传导高频信号@@@@,因此@@接地@@@@层@@的@@开口上@@将出现感应压降@@。对@@于典型的@@@@ ECL或@@ TTL 信号@@,此压降可能大于数百毫伏@@,足以严重影响@@ 12 位@@、10 MHz 转换器或@@@@ 8 位@@、20-MHz 转换器的@@性能@@。简单的@@补救方法是在@@接地@@@@层@@的@@切口上@@添加一@@根导线@@,使环路面积保持较小@@。

电源干扰是另一@@个值得关注的@@问题@@。电源线的@@特性阻抗必须尽可能低@@。为使此比值较小@@,需要使接地@@@@层@@始终位@@于@@电源线下方@@,以便降低电感并提高@@电容@@。有选择地@@将旁路电容放在@@关键位@@置上@@@@,可以进一@@步提高@@电容@@。如果只顾及到电容@@,例如将@@ 0.1 µF 电容放在@@电源引脚上@@以降低其阻抗@@,则电感为@@ 30 nH 的@@电源线在@@每次瞬变之后将具有大约@@ 3MHz 的@@阻尼振荡@@。

免责声明@@:本文为网@@络转载文章@@,转载此文目的@@在@@于传播相关技术@@知识@@,版权归原作者所有@@,如涉及侵权@@,请联系小编删除@@(联系邮箱@@:service@eetrend.com )。