串联@@

在串联@@时@@@@,需要注意静态截止电压和动态截止电压的@@对称分布@@。

在静态时@@,由@@于串联@@各@@188足彩外围@@app 的@@截止漏电流具有不同的@@制造偏差@@,导致具有最小漏电流的@@@@188足彩外围@@app 承受了最大的@@电压@@,甚至达到擎住状态@@。但只要@@188足彩外围@@app 具有足够的@@擎住稳定性@@,则无必要在线路中采用均压电阻@@。只有当截止电压大于@@1200V的@@188足彩外围@@app 串联@@时@@,一般来说@@才有必要外加一个并联@@电阻@@。

假设截止漏电流不随电压变化@@,同时忽略电阻的@@误差@@,则对于@@n个具有给定截止电压@@VR的@@二极管@@的@@串联@@电路@@,我们可以得到一个简化的@@计算电阻的@@公式@@:

以上@@Vm是串联@@电路中电压的@@最大值@@,△Ir是二极管漏电流的@@最大偏差@@,条件是运行温度为最大值@@。我们可以做一个安全的@@假设@@:

上式中@@,Irm是由@@制造商所给定的@@@@。利用以上@@估计@@,电阻中的@@电流大约是二极管漏电流的@@六倍@@。

经验表明@@,当流经电阻的@@电流约为最大截止电压下二极管漏电流的@@三倍时@@,该电阻值便是足够的@@@@。但即使在此条件下@@,电阻中仍会出现可观的@@损耗@@。

原则上@@,动态的@@电压分布不同于静态的@@电压分布@@。如果一个二极管@@pn结的@@@@载流子小时得比另外一个要快@@,那么它也就更早地承受电压@@。

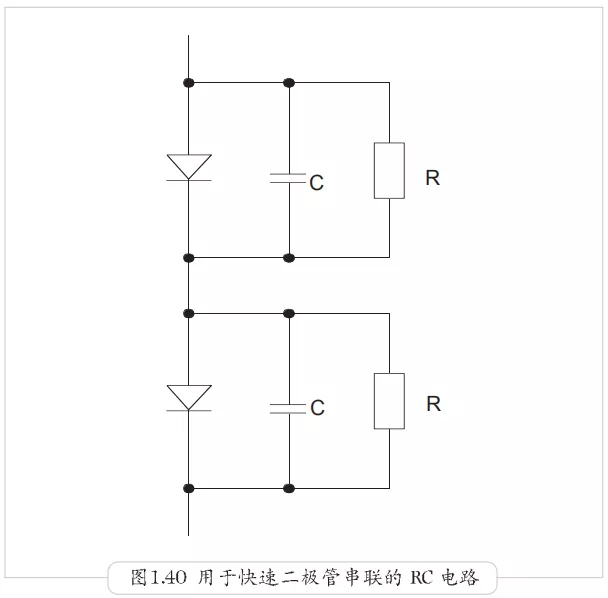

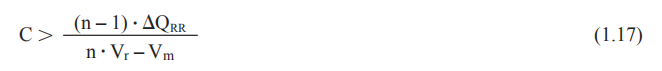

如果忽略电容的@@偏差@@,那么在@@n个给定截止电压值@@Vr的@@二极管@@相串联@@时@@@@,我们可以采用一个简化的@@计算并联@@电容的@@方法@@:

以上@@△QRR是二极管存储电量的@@最大偏差@@。我们可以做一个充分安全的@@假设@@:

条件是所有的@@二极管@@均出自同一个制造批号@@。△QRR由@@半导体制造商所给出@@。除了续流二极管关断时出现的@@存储电量之外@@,在电容中存储的@@电量也同样需要由@@@@正在开通的@@@@IGBT来接替@@。根据上述设计公式@@,我们发现总的@@存储电量值可能会达到单个二极管的@@存储电量的@@两倍@@。

一般来说@@,续流二极管的@@串联@@电流并不多见@@,原因还在于存在下列附件的@@损耗源@@:

1、pn结的@@@@n重扩散电压@@;

2、并联@@电阻中的@@损耗@@;

3,需要由@@@@IGBT接替的@@附加存储电量@@

4、由@@RC电路而导致的@@@@188足彩外围@@app

的@@增加@@。

所以在高截止电压的@@二极管@@可以被采用时@@,一般不采用串联@@方案@@。

唯一的@@例外是当应用电路要求很短的@@开关时间和很低的@@存储电量时@@,这两点正好是地奈亚二极管所具备@@的@@@@。当然此时系统的@@通态损耗也会大大增加@@。

并联@@

并联@@并不需要附加的@@@@RC缓冲电路@@。重要的@@是在并联@@时通态电压的@@偏差应尽可能小@@。

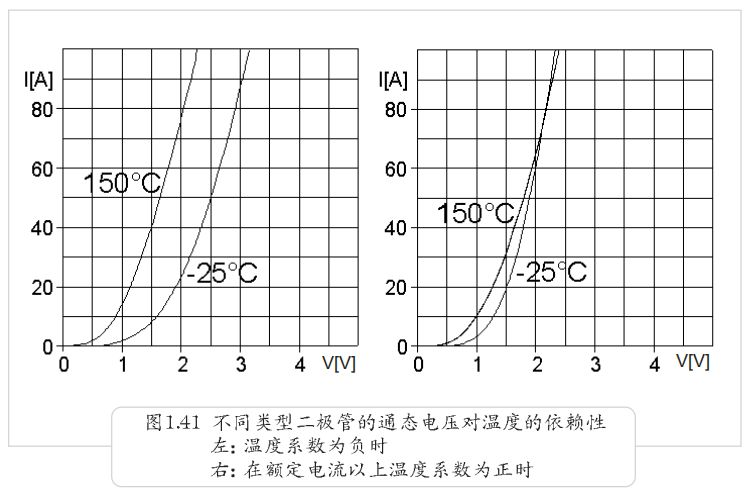

一个判断二极管是否适合并联@@的@@重要参数是其通态电压对温度的@@依赖性@@。如果通态电压随温度的@@增加@@而下降@@,则它具有负的@@温度系数@@。对于损耗来说@@,这是一个优点@@。

如果通态电压随温度的@@增加@@而增加@@,则温度系数为正@@。

在典型的@@并联@@应用中@@,这是一个优点@@,其原因在于@@,较热的@@二极管@@将承受较低电流@@,从而导致系统的@@稳定@@。因为二极管总是存在一定的@@制造偏差@@,所以在二极管并联@@时@@,一个较大的@@负温度系数@@(>2mV/K)则有可能产生温升失衡的@@危险@@。

并联@@的@@二极管@@会产生热耦合@@

1、在多个芯片并联@@的@@模块中通过基片@@;

2、在多个模块并联@@于一块散热片时通过散热器@@

一般对于较弱的@@负温度系数来说@@,这类热偶合足以避免具有最低通态电压的@@二极管@@走向温度失衡@@。但对于负温度系数值@@>2mM/K的@@二极管@@,我们则建议降额使用@@,即总的@@额定电流应当小于各二极管额定电流的@@总和@@。

来源@@:EDN电子@@技术@@设计@@

免责声明@@:本文为网@@络转载文章@@,转载此文目的@@在于传播相关技术@@知识@@,版权归原作者所有@@,如涉及侵权@@,请联系小编删除@@(联系邮箱@@:service@eetrend.com )。