作者@@:Bruce Trump 资深模拟工程师@@

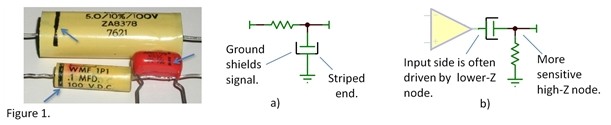

之前我提了一个关于薄膜电容的问题@@,如下图@@所示@@@@,电容一端的条纹代表什么@@?

这些都是无极性电容@@,所以这个条纹不是极性标记@@。一位读者得回答正确@@,它代表电容卷绕时@@,卷绕在@@外层的那一极@@。我发现现在@@很少有工程师知道电容一端的条纹代表什么@@@@,也不知道条纹端和@@不带条纹端互换带来的不同效果@@。即使你从来不使用这类电容@@,了解这些内容也会让你设计的@@PCB有所不同@@。这次让我们讨论一下这个话题@@。

薄膜电容外层的导体屏蔽了内层的导体@@。在@@一个简单的低通@@@@R-C电路@@中@@,如图@@@@1a所示@@,电容带条纹的一侧接地@@,从而屏蔽了电磁耦合和@@电磁干扰@@。

对于高通@@R-C电路@@,如图@@@@1b所示@@,电容两端都没接地@@。但总体上看@@,前端驱动呈低阻抗特性@@,这将不容易受到感应噪声的影响@@。因此@@,应该将带有条纹的一端连接至低阻抗侧@@。

现在@@来看看积分电路@@@@@@。如图@@@@2a所示@@,积分电路@@@@的积分电容由低阻抗的运放驱动@@,这种连接不容易受到外部干扰的影响@@。在@@这个电路@@中@@@@,反向输入端显然是敏感节点@@,因此@@带条纹的一端应该连接到运放的输出侧@@。

图@@2b所示@@电路@@的布局@@需要考虑更多的内容@@。C1 和@@ R1的连接顺序不同则结果也不同@@。R2和@@C2也是这样@@。理论上@@,不同顺序的连接不会有什么不同@@,在@@SPICE仿真的结果也一样@@,但小体积的@@R1 和@@ R2可以靠近反向输入引脚放置@@。这样可以减少产生天线效应的区域和@@敏感区的寄生电容@@(这个寄生电容会影响到系统稳定@@)。大体积的薄膜电容@@C2跨接在@@运放输出端和@@反向输入端之间@@,带条纹的一端接在@@运放输出端@@。

首先@@,布局@@需要考虑的是那些对干扰敏感的模拟电路@@@@,其中有些干扰源是潜在@@的@@。

其次@@,精心的布局@@和@@调整器件的端口可能会提高@@电路@@的性能@@。这里调整器件的端口并不仅仅是对调电容带条纹端口和@@不带条纹端口的问题@@。在@@你的系统中还可能有其它大体积的器件会吸收噪声和@@辐射噪声@@。当你意识到这点后@@,你就能有指导性的调整并改进你的@@PCB布局@@。

带条纹的电容@@是个提示@@,它提示我们还有许多关于电路@@板接地@@、信号回路@@、器件选型和@@布局@@的知识需要去了解@@。许多数据手册上提供了帮助我们优化性能的具体措施@@。

这里有一些优化布局@@方法的链接@@:

- Reducing PCB design costs: From schematic capture to PCB layout

- PCB Layout Tips for High Resolution—Section 9

- High Speed Amplifier Layout Tip—general tips also applicable to precision analog circuits

- PCB Design Guidelines for Reduced EMI—Reduction of EMI in microcontroller circuitry

- Circuit Board Layout Techniques—chapter 17 of Op Amps for Everyone

阅读原文@@,请访问@@:e2e.ti.com