首发@@ I EDN电子@@技术@@设计@@@@

近年来随着高性能计算需求的@@持续增长@@,HBM(High Bandwidth Memory,高带宽存储器@@)总线接口被应用@@到越来越多的@@芯片产品中@@,然而@@HBM的@@layout实现完全不同于传统的@@@@Package/PCB设计@@,其基于@@2.5D interposer的@@设计@@中@@,由于@@interposer各层厚度@@非常薄且信号线细@@,使得直流损耗@@、容性@@负载@@、容性@@/感性耦合等问题严重@@,给串扰和插损指标带来了非常大的@@挑战@@。

为应对这些挑战@@,传统上可以通过参数化建模进行大量例子扫描迭代仿真@@,来确定合适的@@@@方案@@。但由于@@@@HBM设计@@方案可变化的@@方式非常多@@,使得扫描仿真的@@工作量很大@@,同时大量的@@扫描仿真也对仿真计算资源和产品交付时间造成了很大的@@压力@@。

本篇文章将针对上述@@HBM设计@@挑战和传统仿真流程上的@@问题@@,提出相应的@@解决方案@@。

HBM仿真实例@@

HBM仿真设计@@的@@关键在@@于@@,确定合适的@@@@interposer出线类型@@。HBM的@@出线类型@@仿真@@确认流程在@@行业里有两种方式@@:

1)前仿真确认@@,即@@仿真工程师@@创建参数化的@@@@HBM出线类型@@仿真@@,通过仿真确认最佳出线类型@@@@,并反馈给@@layout工程师@@实现@@。相对来说效率较高@@,可尝试大量的@@出线类型@@进而选择更好的@@@@。这是@@一种主流的@@方式@@。

2)后仿真确认@@,即@@layout工程师@@做多种不同的@@设计@@用于仿真@@。相对来说效率较低@@,可尝试的@@出线类型@@数量有限@@,难以获得最佳值@@。本文将不做讨论@@。

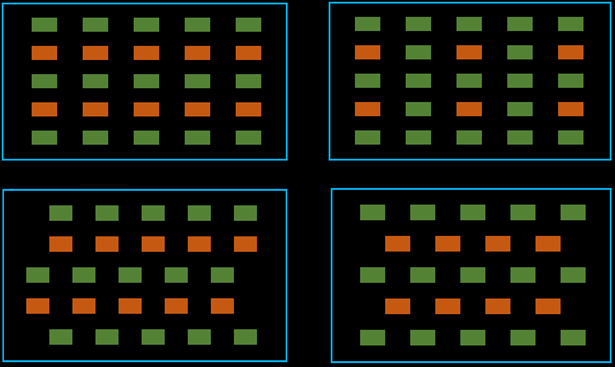

上图@@@@1是@@4种简化的@@@@HBM出线类型@@截面@@示意图@@@@,这个设计@@方案中有@@5层金属层@@,其中褐色为信号@@,绿色为@@GND。从这@@4种出线类型@@中可以看到@@,信号和@@GND分布的@@位置是@@不同的@@@@,对应的@@性能也会有所不同@@。这些位置信息可以定义为变量信息@@,而位置的@@变化就是@@变量的@@取值@@,因此@@,需要进行扫描仿真来判断最佳位置@@。HBM的@@出线类型@@相关的@@变量可达十几种@@,比如@@:信号金属宽度@@@@/厚度@@、GND金属宽度@@、相对位置@@、介质厚度@@@@、纵向@@GND处理方式等@@。各种变量在@@不同的@@取值组合下@@,相应地@@、迭代的@@@@case数量会达到几百种甚至更多@@,这需要在@@前仿真中完成@@@@。因此@@,传统方法上获得一个较好的@@出线类型@@有很大工作量和仿真时间需求@@。

如何在@@有限的@@时间内@@,在@@仿真少数@@case的@@情况下@@,就找到较好的@@答案@@?

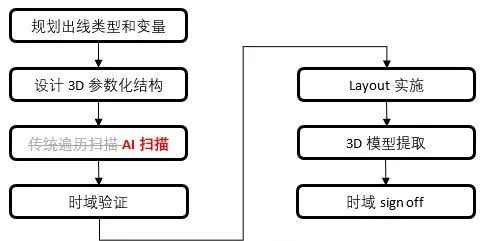

Cadence Optimality Intelligent System Explorer 的@@AI算法@@在@@下图@@@@@@2的@@HBM仿真设计@@流程中替代了传统的@@遍历扫描@@,实现了@@AI智能参数化判别扫描@@,来加速迭代结果收敛@@。应用@@AI算法@@使得计算几十个例子所得的@@结果就能达到传统数百个参数化仿真迭代的@@@@效果@@。

图@@2 HBM仿真设计@@流程图@@@@

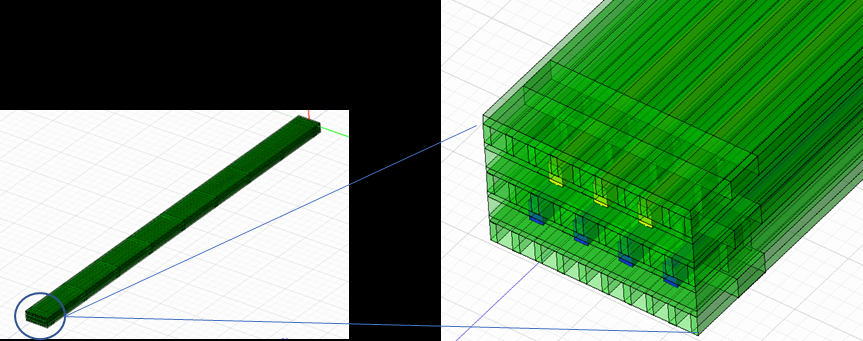

根据用户计划仿真的@@@@HBM 出线类型@@和对应的@@变量@@,将其在@@@@Cadence Clarity 3D Workbench中创建出@@HBM 3D结构@@图@@@@,如下图@@@@@@3。注意@@:所有需要参与参数化仿真的@@结构@@都要定义为变量@@,比如@@:金属线宽度@@。

图@@3 HBM 3D结构@@

完成@@HBM 3D结构@@设计@@@@、仿真端口频率等设置后@@,在@@Optimality Explorer界面中勾选相关参与扫描的@@变量@@,并对变量取值范围进行定义@@。变量取值类型支持连接值@@、离散值@@、数组三种类型@@,如下图@@@@@@4。离散和数组类型是@@因为在@@生产中有些结构@@只有固定几种选项可以选择@@,比如@@:介质厚度@@@@、金属厚度@@@@。

图@@4参数扫描定义@@

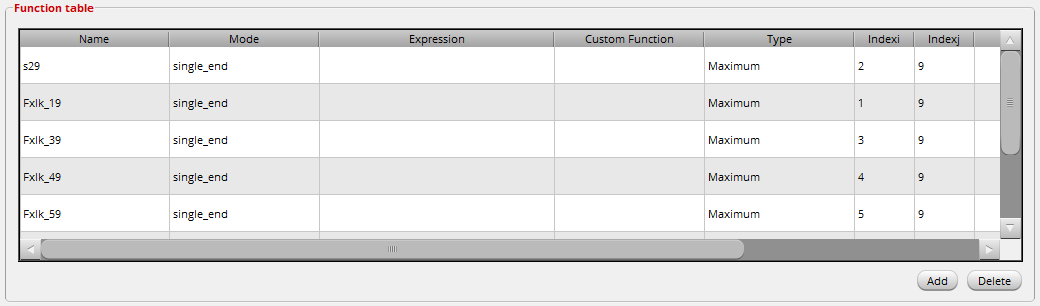

完成@@变量参数定义后@@,接着定义相应端口的@@插损@@、串扰相关表达式及收敛目标函数@@,如下图@@@@@@5,以便用于@@AI仿真收敛@@。

图@@5定义收敛目标函数@@

下图@@@@6为仿真结果收敛记录图@@表@@。从图@@表上可以看到第@@29次的@@时候已经获得非常好的@@值@@,这时用户就可以停止本次仿真或@@者先用第@@29次的@@结果作下一步的@@仿真@@。Optimality Explorer支持多@@case并行仿真@@,以进一步减少仿真时间@@。

图@@6收敛纪录图@@表@@

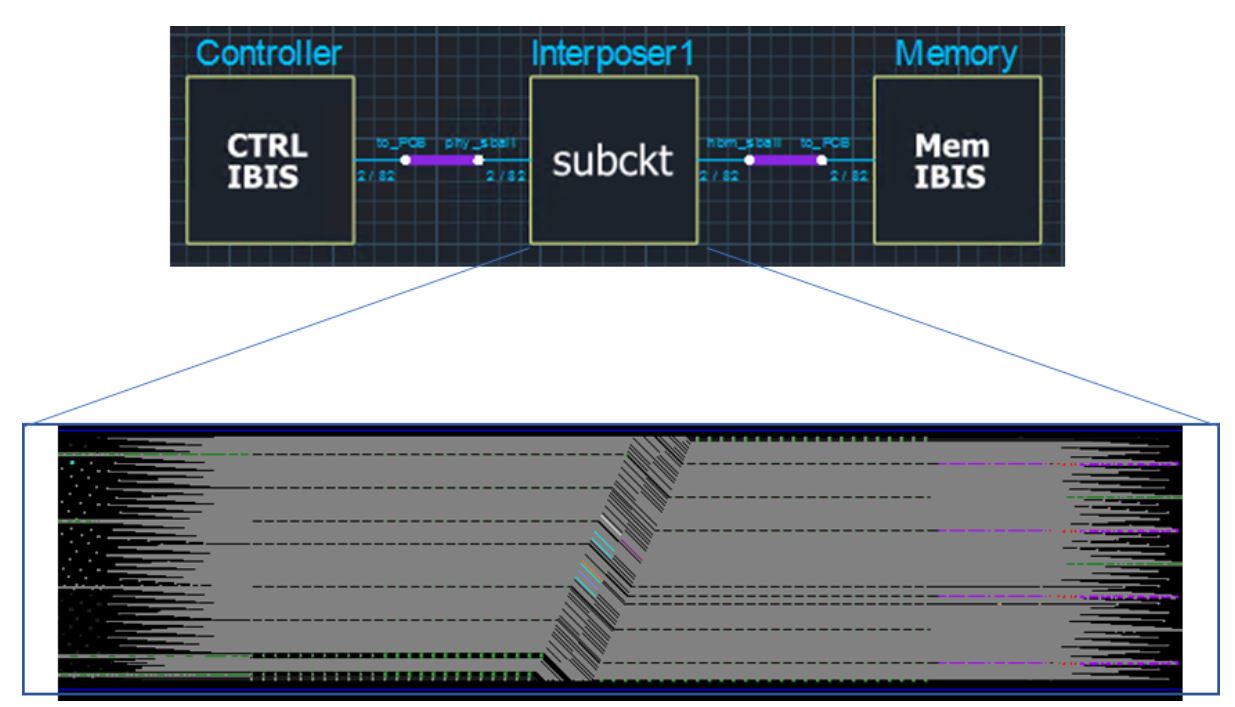

将优化@@完成@@的@@@@HBM 出线类型@@对应的@@@@S参数在@@时域里验证@@,如果能满足要求@@,则将对应的@@参数传递给@@interposer layout工程师@@,并根据这些参数完成@@最终@@的@@@@HBM设计@@。最终@@,设计@@好的@@@@HBM layout导入@@Clarity 3D Solver中再次提取模型@@,并加载到@@Cadence Sigrity Topology Explorer(TopXP)中进行最后的@@时域眼图@@仿真@@,如下图@@@@@@7。

图@@7时域链路@@

总结@@

本例中应用@@了@@Cadence 公司的@@@@Optimality Explorer优化@@,其内嵌@@AI算法@@,并与@@Clarity 3D Solver的@@参数化仿真结合@@,帮助用户快速收敛结果@@。Optimality Explorer具有极强的@@样本有效性@@,只需较少地迭代次数@@,即@@可得到一个较好的@@结果@@。内部@@AI优化@@算法@@通过基于目标函数的@@前期评估结果建立替代函数@@(概率模型@@),来找到最小化目标函数的@@值@@。该@@AI算法@@与传统随机或@@网@@格搜索的@@不同之处在@@于@@,它在@@尝试下一组超参数时@@,会参考前期的@@评估结果@@,因此@@可以省去很多无用功@@,最终@@达到快速收敛的@@效果@@。

本文转载自@@: Cadence楷登@@PCB及封装资源中心@@