自@@TechInsights于@@2021年底推出电源管理@@集成电路@@@@(PMIC)工艺@@分析频道以来@@,已分析了多种器件@@。内容囊括@@高压栅极驱动器@@和@@汽车级电源转换@@@@IC,乃至@@移动电源管理@@集成电路@@@@。据观察@@,越来越多的制造商尝试以共@@同封装@@配置或@@与@@硅@@IC本身@@“全集成@@”的方式将无源@@@@188足彩外围@@app 集成至电源管理@@集成电路@@产品@@。

与@@所有电力电子@@产品一样@@,尺寸@@、重量和@@功率@@(SWaP)均为关键的性能指标@@。为提高@@系统效率@@,我们需要更小巧轻便且功率密度更高的系统@@。在@@电源管理@@集成电路@@运行功率水平相对较低的情况下@@,集成是非常理想的方式@@,并且具备@@理论可行性@@。

一种@@“集成稳压器@@”(IVR)受到了特别关注@@。鉴于@@相对较小的变化也可能损坏@@CPU等精密部件中的精密晶体管@@,所以需使用稳压器电路提供稳定的恒电压@@。

许多消费类电子@@产品的输入电压为@@12 V(最新的服务器架构为@@48 V)。产品内部的最终@@“负载点@@”(PoL)的降压转换@@过程为@@CPU、GPU和@@其他内部@@188足彩外围@@app 提供其所需的电压@@(通常@@<2 V)。随着架构复杂化@@,需输入不同电压@@,因而需采用多个@@稳压器电路提供不同的电压@@,而它们会占用宝贵的电路板空间@@@@。集成此项功能将带来明显收益@@。

“全集成@@”稳压器的早期尝试@@

迄今为止@@,英特尔公司对这项技术@@的@@尝试或@@许最为瞩目@@。英特尔尝试在@@第@@4代和@@第@@5代核心微处理器@@(Haswell和@@Broadwell)上采用所谓的@@“全集成@@稳压器@@@@”(FIVR)解决方案@@。在@@2014年亚太经合组织会议上提交的一篇论文@@展示了这种方法@@——将非磁性电感集成至栅格阵列@@(LGA)封装@@。一篇在@@@@2016年提交的研究论文@@显示了研讨中的不同电感的更多详情@@,包括非耦合螺线管@@、交错螺线管@@、屏蔽电镀通孔@@(PTH)环和@@@@3DL。该论文得出结论@@,未来可能必须使用磁性材料以满足电流密度需求@@。2011年的早期演示@@展示了对片上电感的研究@@,包括磁性@@CoZrTa包络@@。

从第六代产品开始@@,英特尔放弃了全集成@@稳压器@@@@方案@@,原因之一似乎是这种方法会使@@CPU附近产生额外热量@@。传闻这项技术@@将被再次引入@@,正如在@@@@VLSI 2022上的演示@@所证明的那样@@,英特尔仍在@@以某种形式研究这一概念@@。

苹果@@APL1028集成稳压器@@

我们的拆解频道详细报道了已发布的最重要的消费类电子@@产品@@。根据对采用@@M1处理器的@@2021款@@MacBook Pro(16英寸@@)的分析@@,我们发现苹果@@@@APL1028芯片被设置在@@@@M1处理器区@@域散热外壳内的@@PCB背面@@。此后@@,我们编写了一份有关该器件的@@电源管理@@集成电路@@工艺@@分析报告@@,并在@@最近的@@电源管理@@集成电路@@简报@@中重点介绍了集成电感技术@@@@。

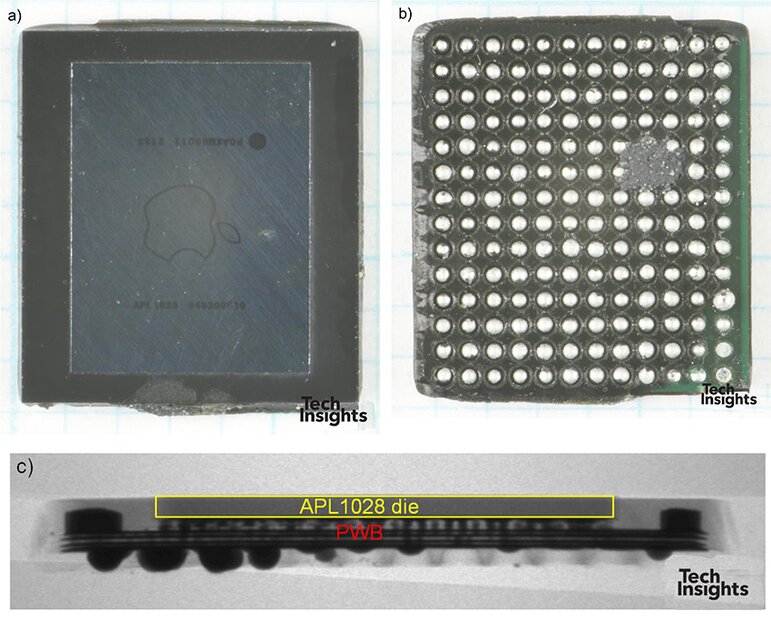

如图@@@@1所示@@,APL1028采用倒装芯片球栅阵列@@(FCBGA)封装@@。

图@@1:倒装芯片球栅阵列封装@@的@@苹果@@@@APL1028集成稳压器@@:a)俯视图@@@@b)仰视图@@@@c)突出显示芯片的侧视@@x光片@@

当使用酸解封工艺@@取出封装@@中的芯片后@@,获得集成电路@@,分析表明这很可能采用了台积电的@@12 FF工艺@@。注意@@,这并非@@BCD电源管理@@集成电路@@,传统@@双极器件或@@@@DMOS功率晶体管与@@鳍式场效晶体管@@(FinFETs)的集成需要使用大量昂贵的光刻掩模@@。假设这些部件在@@相对较低的功率水平下运行@@,则仅使用鳍式场效晶体管即可@@。我们迄今发现的最小的@@“传统@@”电源管理@@集成电路@@逻辑节点约为@@55 nm,同样来自@@@@去年报道@@的苹果@@产品@@。

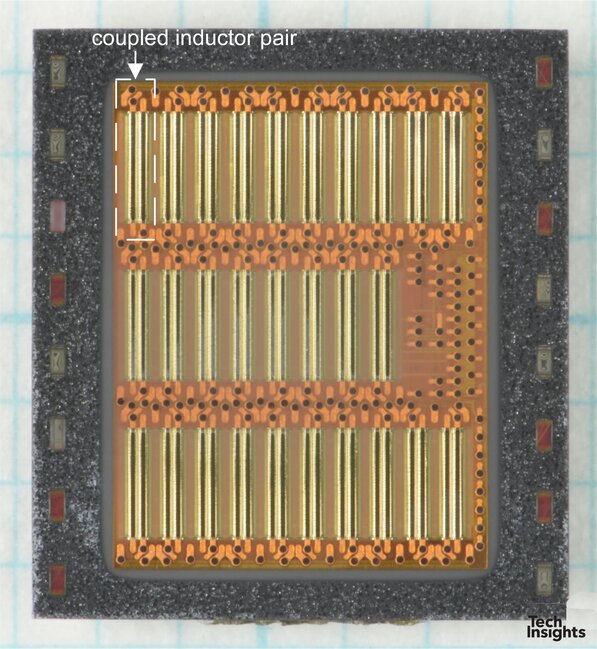

随着封装@@的@@去除@@,将逐渐展现真正的创新@@。图@@2显示了采用抛光和@@@@O2蚀刻工艺@@后的封装@@@@。图@@中显示了三排耦合电感@@(共@@28个@@)。

图@@2:抛光封装@@@@(显示片上电感区@@域@@)

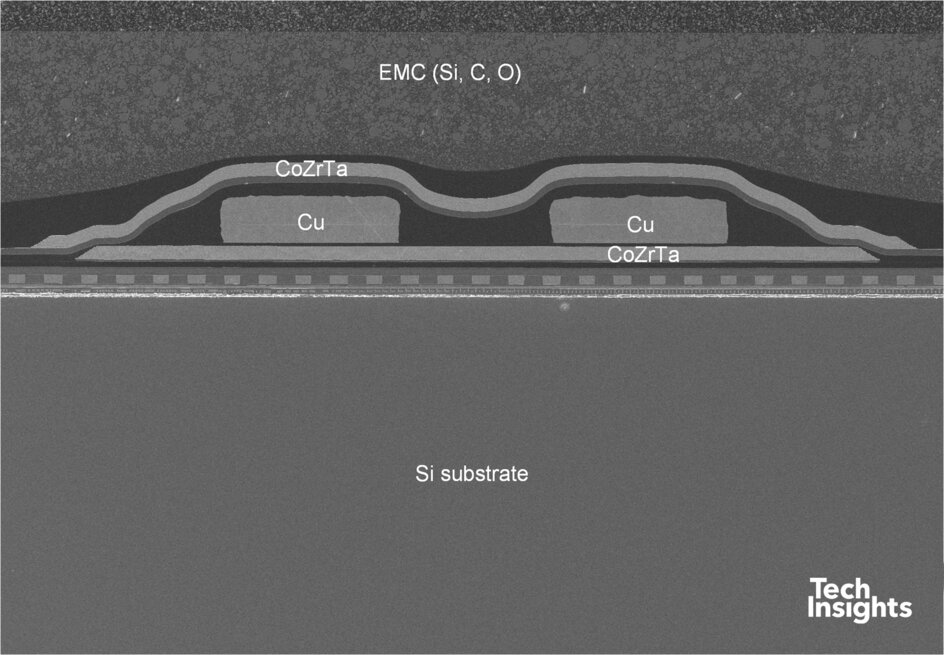

如图@@@@3所示@@,每个@@耦合电感均设置在@@器件的@@RDL区@@,两个@@铜条外部包绕磁性材料制成的包络@@@@。各铜条的一端通过过孔与@@芯片相连@@,而另一端向外连接至封装@@@@。

图@@3:APL1028芯片的扫描电镜剖面图@@@@(显示带磁性包络@@的耦合电感@@)

这与@@@@2011年的英特尔研究论文中提出的概念相似@@@@,甚至电感包络@@中似乎使用了相同的@@CoZrTa磁性材料叠层@@。苹果@@已将这一概念应用于@@生产器件@@。

来自@@安普沃尔@@半导体@@(Empower Semiconductor)的另一集成稳压器@@示例@@

我们最近发布了一份关于@@@@安普沃尔@@EP7037C三路输出集成稳压器@@的@@电源管理@@集成电路@@工艺@@分析报告@@。该产品允许通过多个@@不同的稳压为器件的不同部件供电@@。安普沃尔@@甚至更进一步@@,于@@最近发布了@@四路输出器件@@——EP71xxx系列@@。安普沃尔@@声称其集成稳压器@@技术@@可将体积缩小@@10倍@@,同时将运行速度提高@@@@1000倍@@。产生这种改进的原因在@@于@@传统@@的稳压器需要较大的输出电容来充分过滤瞬态响应@@。安普沃尔@@声称其解决方案@@允许处理器电源状态发生纳秒级变化@@。

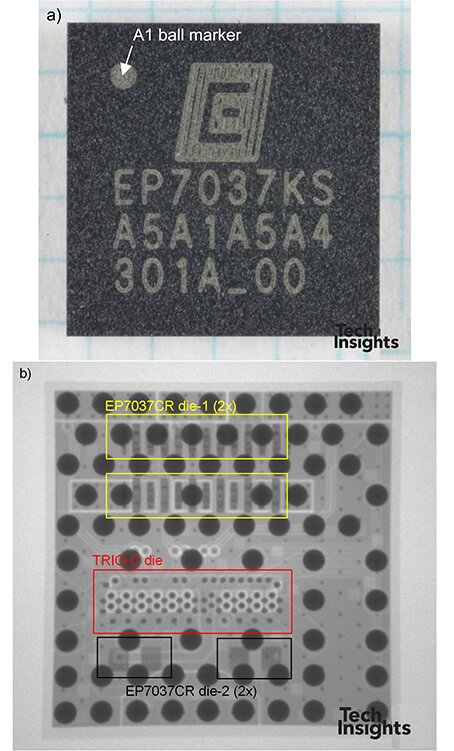

图@@4显示了翻转芯片球形栅格阵列封装@@@@和@@@@x光片@@,其中显示了@@“TRIO-C”IC芯片以及另外四个@@硅深沟槽电容器芯片的位置@@。

图@@4:安普沃尔@@EP7037C集成稳压器@@a)翻转芯片球形栅格阵列封装@@@@b)封装@@的@@x光片@@

该产品与@@这篇@@188金宝搏@@ 前文讨论的苹果@@@@APL1028集成稳压器@@有部分相似@@之处@@。与@@APL1028相似@@,我们认为图@@中的@@“TRIO-C”芯片很可能基于@@台积电的@@12 FF工艺@@制程@@。但其集成方法不同@@,图@@中没有采用片上电感@@。相对地@@,安普沃尔@@提供了两种解决方案@@@@:

定制服务@@,安普沃尔@@将协助设计@@待集成@@PCB的专用电感走线@@。

安普沃尔@@还提供@@EP7037B,其中包含一个@@由翻转芯片球形栅格阵列封装@@@@缠绕的电感器@@。

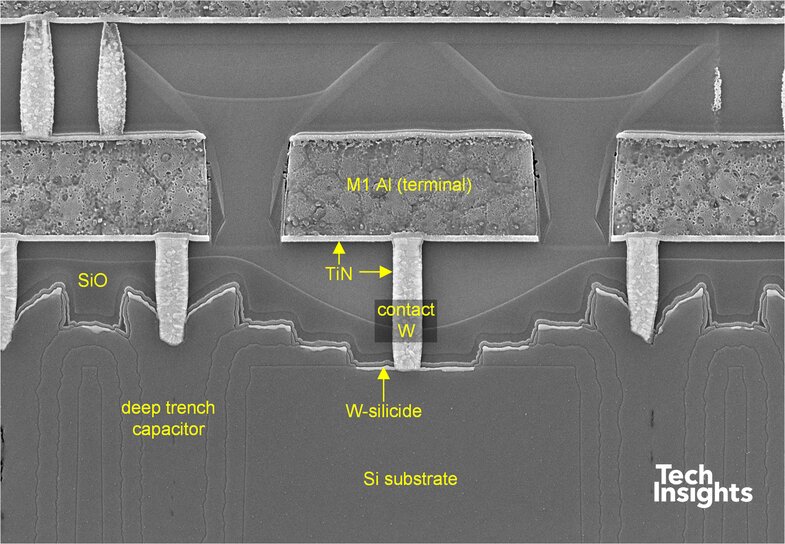

采用另外四个@@硅深沟槽电容器芯片是减少额外的无源@@188足彩外围@@app 和@@缩小电路板空间@@的另一种@@方法@@。图@@5显示了此类芯片之一的扫描电镜剖面@@。采用硅化钨触点的双金属铝工艺@@与@@填充多晶硅并形成电容器的深沟槽相连@@。

图@@5:硅深沟槽电容的硅扫描电镜剖面图@@@@

英飞凌@@集成负载点@@电源@@(IPOL)降压调节器@@

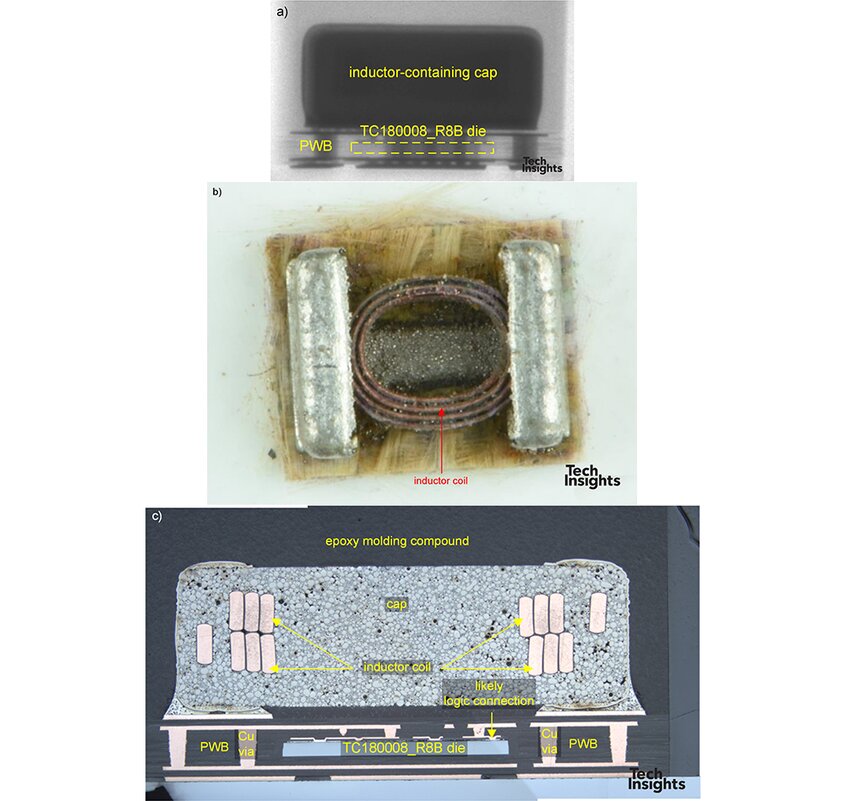

拆去集成稳压器@@后@@,我们可以发现@@,它不仅仅是一个@@用于@@集成无源@@@@188足彩外围@@app 的小众应用@@。英飞凌@@最近发布了@@配备@@@@“全集成@@”4 A降压转换@@器的@@TDM3885集成负载点@@电源模块@@。图@@6中的各图@@像详细描述了@@PG-LGA-15封装@@的@@内部@@,有关更多详情@@,可参见我们@@关于@@该器件的功率封装@@报告@@@@。

图@@6:英飞凌@@TDM3885 IPOL a)标识芯片位置的封装@@侧视图@@@@X光片@@b)显示电感线圈的封装@@喷射蚀刻俯视图@@@@@@c)TC180008_R8B芯片和@@电感线圈的封装@@电镜剖面图@@@@

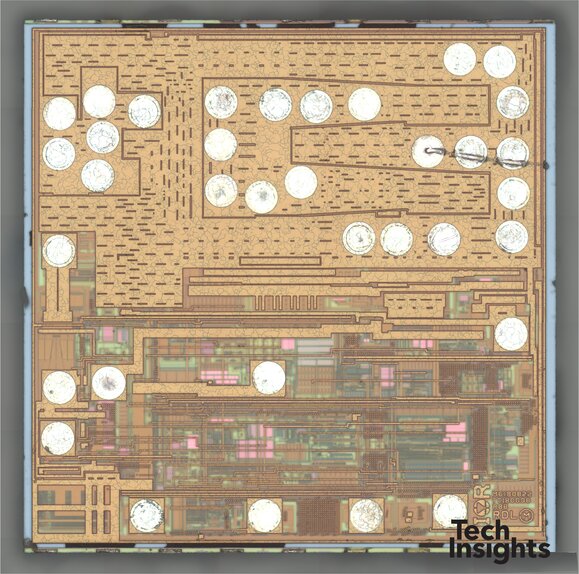

图@@7所示@@的@@TC180008_R8B芯片不含日期标记@@,但因其具有国际整流器标志@@(见右下角@@),所以可合理假设其并非英飞凌@@的新@@IC设计@@。该部件的创新之处在@@于@@电感集成@@,这与@@@@集成稳压器@@非常相似@@@@,可以节省宝贵的电路板空间@@@@。该部件设计@@用于@@电信和@@数据中心等应用的负载点@@电源@@(PoL)转换@@,英飞凌@@指出@@,它适合用于@@@@“空间@@和@@散热受限的应用@@”。英飞凌@@声称@@,因该部件能降低寄生效应@@,所以不但能减少@@80%的电路板面积@@,还能提高@@性能@@。

图@@7:TC180008_R8B芯片图@@@@

总结@@

将无源@@188足彩外围@@app 集成至功率芯片具有明显优势@@。这样能提高@@功率密度@@,尽可能减小电路板空间@@以及缩短物料清单@@(BoM),这些都极具吸引力@@。但这样也会带来各种缺陷@@,并且先前对该技术@@的@@尝试也很快停止了@@。

我们可以观察苹果@@是否将该理念延续至@@M2 Pro和@@Max MacBooks,以及他们在@@散热管理方面如何进行权衡@@。

集成稳压器@@(IVR)绝不是唯一能通过这种方法受益的电源管理@@集成电路@@@@技术@@@@。讨论任何功率转换@@产品时均需重视系统级性能@@,在@@较高的功率下更是如此@@,即使效率稍有提高@@也将变得非常重要@@。当讨论碳化硅@@(SiC)和@@氮化镓@@(GaN)晶体管等新的宽禁带产品@@,需重视这一点@@。分立式晶体管自@@身可能比硅晶体管更昂贵@@,但它们不仅能提高@@晶体管性能@@,无疑还能为更大的系统设计@@节省成本@@。他们通过更高的切换频率来实现这一点@@,从而允许减小电容并提供更便宜轻便且功率密度更高的解决方案@@@@。在@@观察高功率模块时@@,我们逐渐觉察到模块化布局和@@短距互连对降低电感的重要性@@。

完全去除封装@@接线的新型封装@@技术@@示例也在@@不断涌现@@,参见我们关于@@安世半导体@@“铜夹@@”技术@@的@@功率封装@@报告@@,该技术@@去除了低压硅产品@@PSMN3R9 100 V金氧半场效晶体管@@的封装@@接线@@。

对于@@频谱的低功率端和@@电源管理@@集成电路@@@@,我们可以进一步将无源@@器件集成到分立式封装@@中@@,对于@@苹果@@@@APL1028而言@@,实际集成至半导体芯片@@。我们期待在@@未来数年看到相关方面出现突破性进展@@,并且很高兴能继续与@@大家分享我们的发现@@!