本文由@@@@半导体产业纵横@@(ID:ICVIEWS)编译自@@semianalysis

晶体管@@的@@未来@@。

任何芯片的@@基本组成部分都是晶体管@@@@,最近晶体管@@迎来了@@ 75 岁生日@@。今天我们将讨论它的@@下一个@@ 25 年@@。

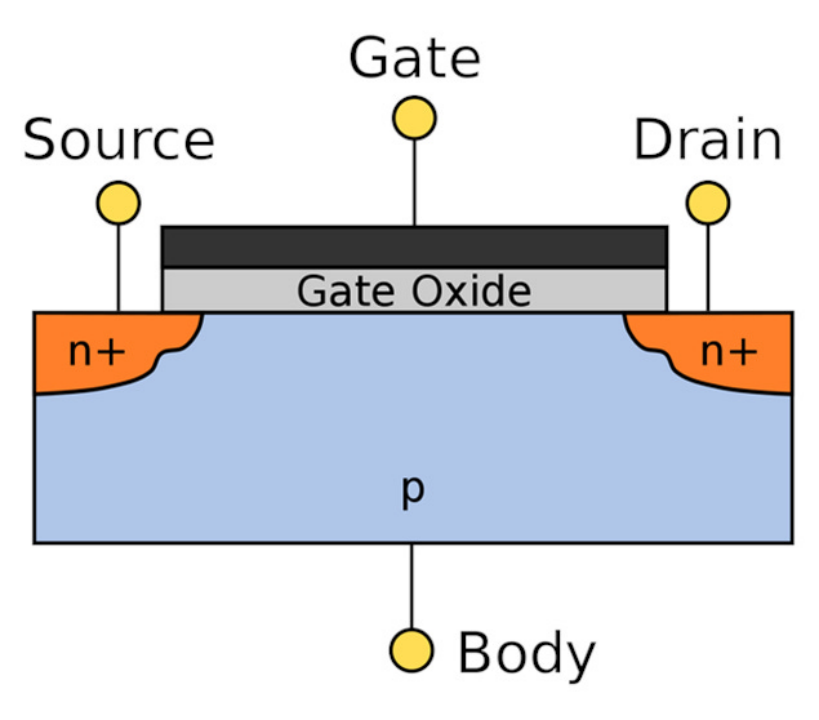

晶体管@@本质上@@是电流开关@@,施加到其@@“栅极@@”的@@电压会导致电流在@@@@“源极@@”和@@“漏极@@”之间的@@通道@@中@@流动@@。每个晶体管@@都可以打开或@@关闭@@,对@@应于@@“1”或@@“0”。在@@摩尔定律扩展和@@@@ CMOS 工艺技术@@改进的@@推动下@@,现代计算芯片在@@数十亿甚至万亿的@@规模上@@做到了这一点@@。

理想的@@晶体管@@可以执行以下@@操作@@:

1.开启时传导最大电流量@@。

2.关闭时不允许任何电流流动@@。

3.尽快切换@@。

晶体管@@的@@三个主要组成部分@@:“栅极@@”、“源极@@”和@@“漏极@@”

晶体管@@简史@@

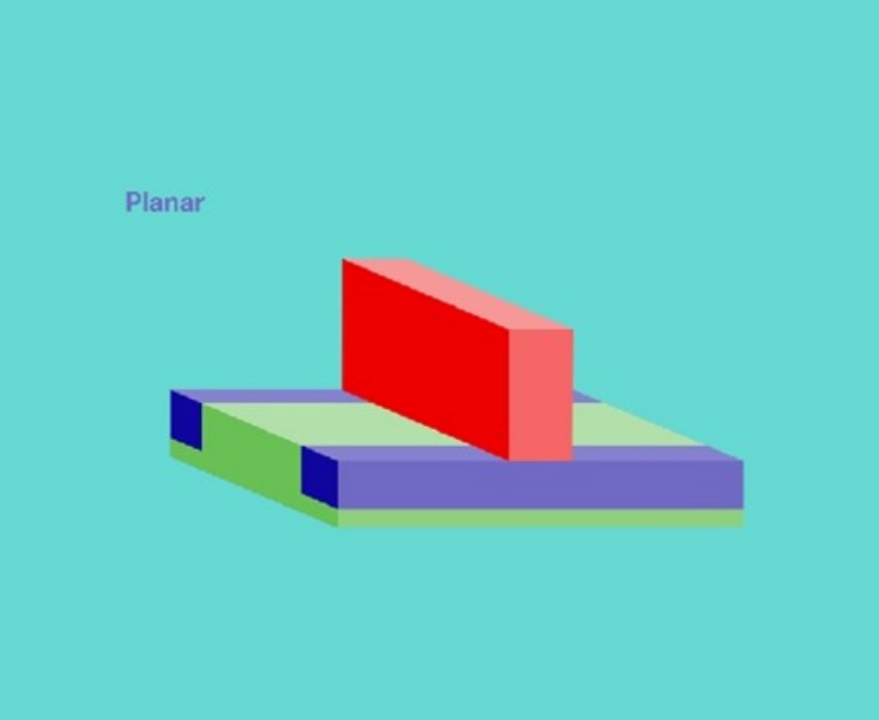

1947 年@@,约翰@@·巴丁@@ (John Bardeen)、威廉@@·肖克利@@ (William Shockley) 和@@沃尔特@@·布拉顿@@ (Walter Brattain) 在@@ AT&T 的@@贝尔实验室发明了第一批晶体管@@@@,称为@@“平面@@”晶体管@@,因为晶体管@@的@@所有@@@@188足彩外围@@app ,包括栅极@@@@、源极@@和@@漏极@@都位于二维@@平面@@上@@@@。

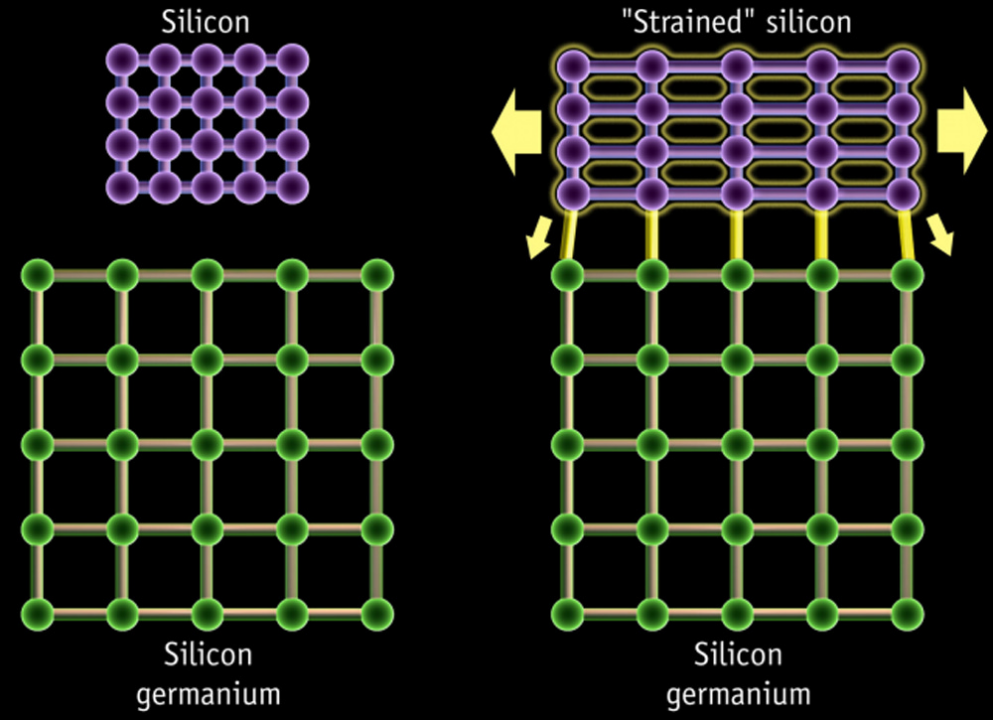

许多迭代以来@@,平面@@晶体管@@的@@开关速度可以通过缩短栅极@@长度来提高@@@@@@。“拉紧@@”硅通道@@也会提高@@@@开关速度@@。为了应变通道@@@@,将一层硅放置在@@一层硅锗@@ (SiGe) 上@@。由@@于硅层中@@的@@原子与@@@@ SiGe 层对@@齐@@,这导致硅原子之间的@@连接拉伸@@,从而使沟道应变@@。在@@这种配置中@@@@,硅原子距离更远@@,干扰电子@@运动的@@原子力减少@@。在@@应变通道@@中@@@@,电子@@迁移率@@(即@@电子@@在@@被电场牵引时的@@移动速度@@)提高@@@@了@@ 70%,从而使晶体管@@开关速度提高@@@@了@@@@ 35%。

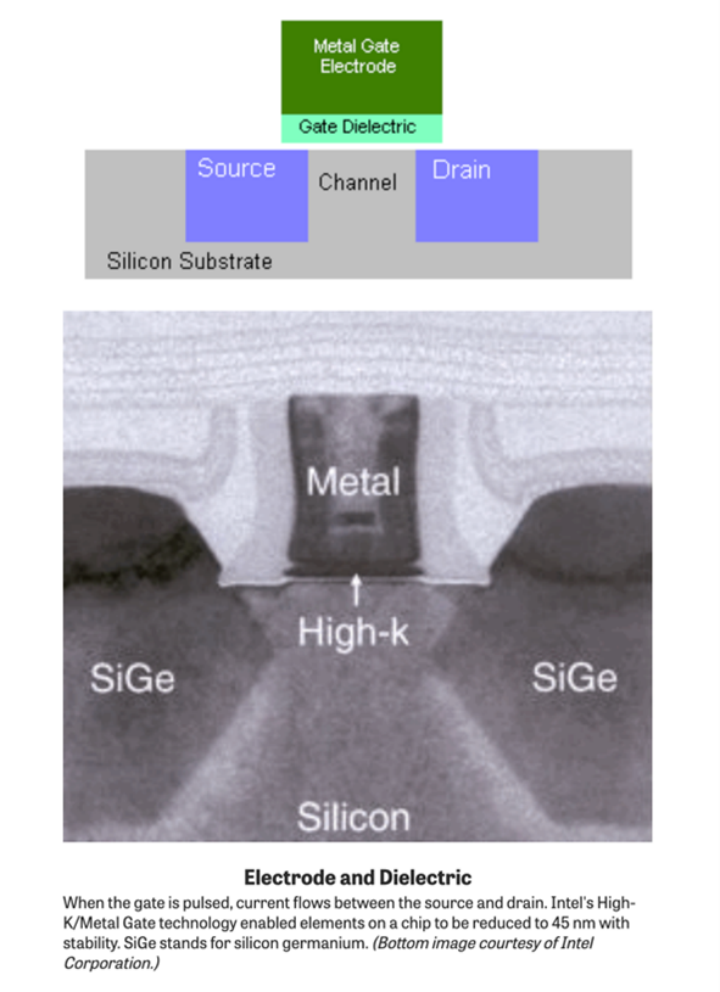

允许继续缩放的@@进一步发展是@@“高@@ K/金属@@”门@@的@@开发@@。在@@ 45nm 节点@@,栅极@@电介质@@开始失去其绝缘@@(介电@@)质量并表现出过多的@@泄漏电流@@(即@@当晶体管@@处于关断状态时@@,大量电流会流过晶体管@@@@)。

栅极@@电介质@@是一个非常薄的@@绝缘层@@,通常由@@二氧化硅制成@@,位于晶体管@@的@@金属@@栅电极和@@电流流过的@@通道@@之间@@。英特尔在@@其@@ 45 纳米工艺@@(2007 年@@)中@@取得重大突破@@,采用铪基介电@@层和@@由@@替代金属@@材料@@组成的@@栅电极@@。三年@@后@@,该行业的@@其他公司也纷纷效仿@@。由@@此产生的@@组合产生了@@“高@@介电@@常数@@”或@@“高@@ K”栅极@@。

随着晶体管@@尺寸的@@不断减小@@,源极@@和@@漏极@@之间的@@空间@@减小到栅极@@失去适当控制沟道中@@电流流动的@@能力的@@程度@@。正因为如@@此@@,平面@@晶体管@@表现出明显的@@@@“短沟道@@”效应@@,尤其是@@在@@@@ 28nm 节点@@以下@@@@,漏电流过大@@。

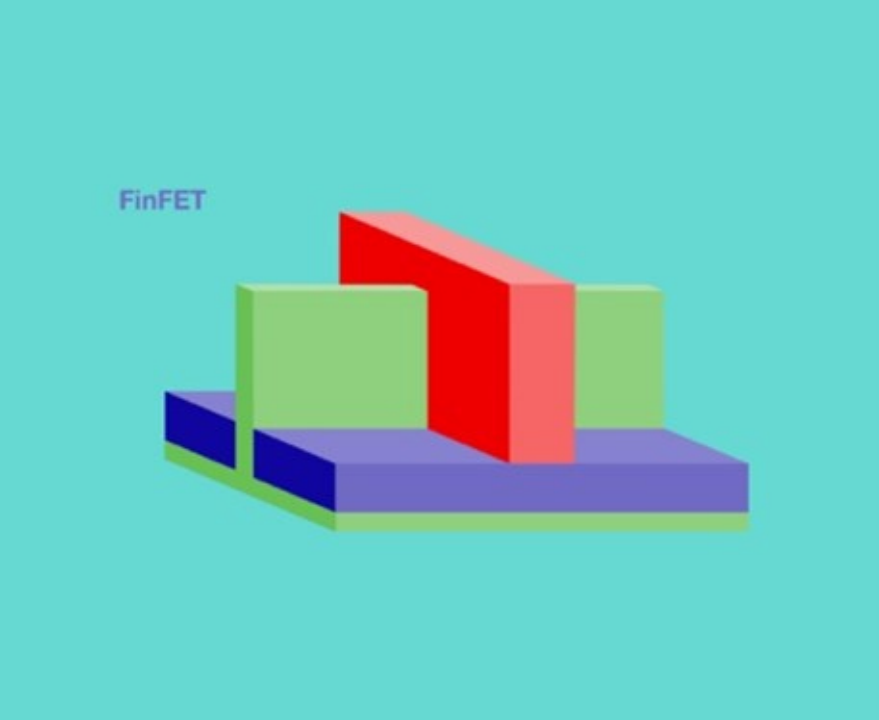

为了应对@@这一挑战@@,业界转向@@@@“3D”晶体管@@,即@@ FinFET。在@@ FinFET 中@@,栅极@@在@@硅鳍的@@三个侧面环绕沟道@@,而不是像平面@@晶体管@@那样仅在@@顶部环绕@@。这样可以更好地控制流过晶体管@@的@@电流@@;FinFET 晶体管@@的@@开关时间明显快于平面@@晶体管@@@@。在@@ 2010 年@@代初期@@,英特尔开始生产@@ 22 纳米节点@@的@@@@ FinFET,而台积电等代工@@厂在@@@@ 3 年@@后开始生产@@ 16 纳米节点@@的@@@@ FinFET。

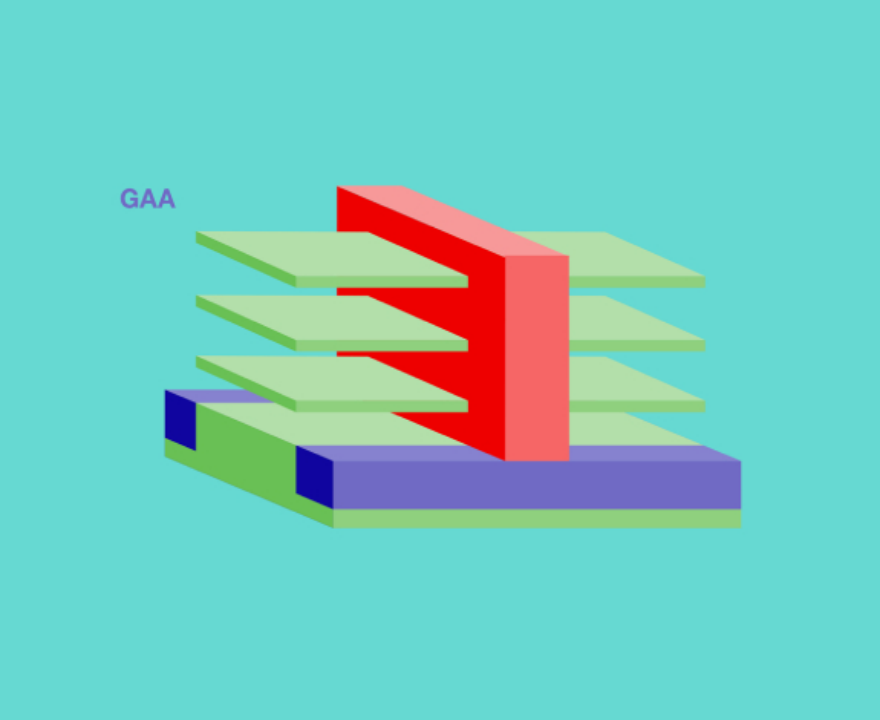

由@@于可以制造多薄@@/多高@@的@@鳍片以及@@可以并排放置多少鳍片的@@限制@@,晶体管@@的@@另一种发展目前正在@@行业中@@进行@@。这些下一代晶体管@@被称为@@@@“Gate-All-Around”晶体管@@,或@@ GAAFET。GAAFET使用堆叠的@@水平@@“纳米片@@”,因此@@栅极@@在@@所有@@@@ 4 个侧面都围绕着通道@@@@。这进一步增加了晶体管@@的@@驱动电流和@@整体性能@@。每个纳米片@@的@@宽度以及@@每个晶体管@@中@@的@@纳米片@@数量@@都可以变化@@,从而允许定制设计@@。

2022 年@@,三星@@开始在@@其@@ 3nm 工艺中@@使用@@ GAA。由@@于良率问题@@,三星@@ 3nm GAP 的@@大批量芯片有@@望在@@@@ 2024 年@@实现量产@@。英特尔的@@@@ 20A 工艺节点@@路线图上@@有@@@@ GAA,该工艺节点@@将于@@ 2024 年@@制造就绪@@,产品将于@@ 2025 年@@批量出货@@。台积电的@@@@ N2 有@@ GAA 2025 年@@或@@@@ 2026 年@@的@@工艺节点@@@@。这些生产年@@份是目标@@,我们认为@@,这些参与@@者中@@至少有@@@@ 2 个可能会进一步延迟@@。

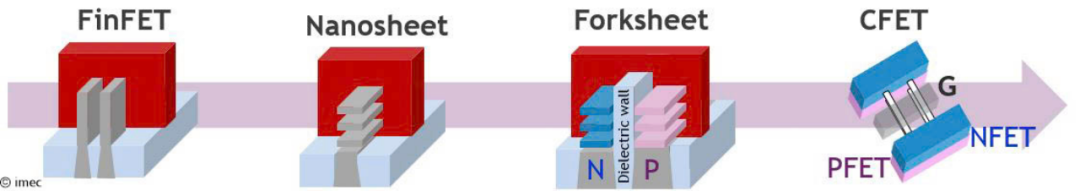

除了最初的@@@@ GAA 工艺之外@@,还包括转向@@@@ forksheet 或@@ 3D 互补@@ FET (CFET),其中@@@@ n 和@@ p 通道@@移动得更近或@@垂直堆叠@@。

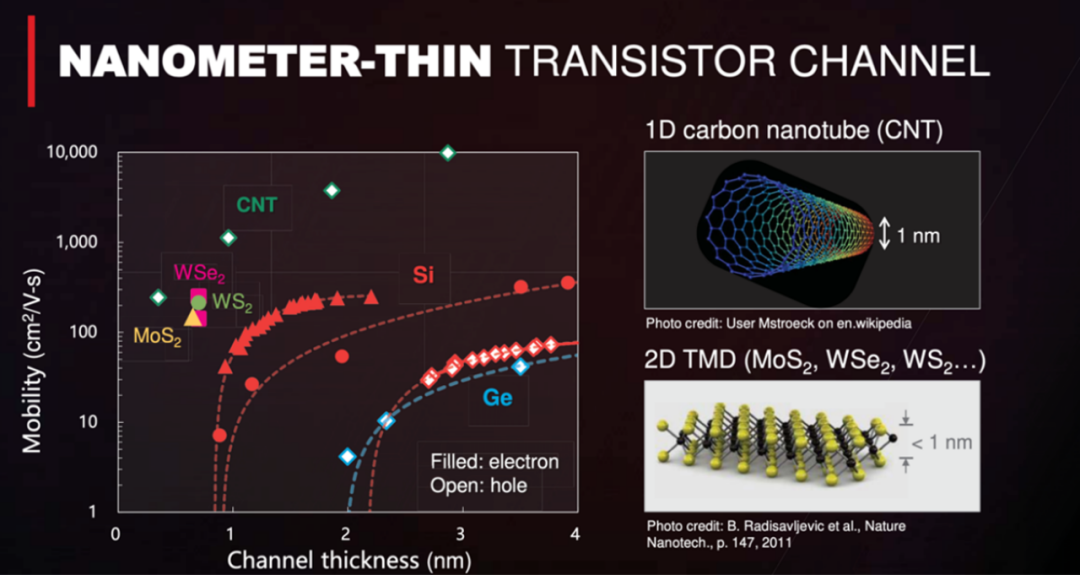

为了继续超越@@ 2nm 的@@路线图@@,向@@ Gate-All-Around 的@@过渡也将需要@@用于@@纳米片@@的@@新晶体管@@通道@@材料@@@@。这是因为硅和@@锗等块状材料@@中@@的@@电子@@迁移率@@显著下降@@ < 5nm。随着我们深入到纳米尺度@@,原子效应@@不再被忽视@@。也许应对@@这些挑战的@@最佳材料@@系列是二维@@材料@@@@@@.。

二维@@材料@@@@

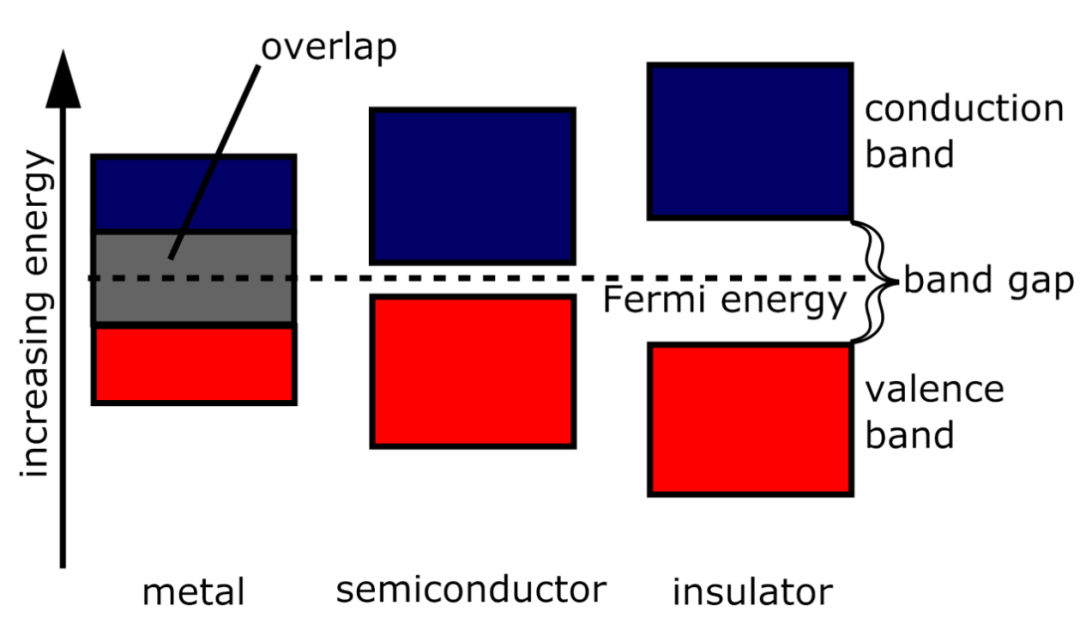

二维@@材料@@@@是由@@单层原子组成的@@结晶固体@@。最著名的@@二维@@材料@@@@是石墨烯@@@@,它是一种碳的@@同素异形体@@,由@@排列在@@六边形晶格中@@的@@单层原子组成@@。但@@是@@,需要@@注意的@@是石墨烯@@没有@@带隙@@。

半导体由@@它们的@@带隙定义@@:将卡在@@价带中@@的@@电子@@激发到它可以导电的@@导带所需的@@能量@@。带隙需要@@足够大@@,以便晶体管@@的@@开和@@关状态之间有@@明显的@@对@@比@@,这样它就可以在@@不产生错误的@@情况下处理信息@@。尽管具有@@@@高@@电子@@迁移率@@@@,但@@没有@@带隙@@,石墨烯@@不能用作半导体材料@@@@。尽管石墨烯@@在@@掺杂时具有@@@@带隙@@,但@@掺杂的@@石墨烯@@不允许足够低的@@关断电流或@@足够高@@的@@导通电流@@。

MoS用于@@下一代纳米片@@的@@最有@@前途的@@二维@@材料@@@@来自@@“过渡金属@@二硫化物@@”或@@“TMD”子系列@@。来自该组的@@材料@@包括二硫化钼@@ (MoS2),TMDs具有@@@@ < 5nm 通道@@厚度所需的@@带隙@@ + 迁移率组合@@。

虽然碳纳米管@@(CNT,一种一维材料@@@@)也受到关注@@,但@@经过@@ 30 多年@@的@@研发@@,它们的@@制造难度仍然很高@@@@。为了实现晶体管@@应用所需的@@性能指标@@,必须生长@@数百万个单独的@@管@@(即@@密度@@)并以相同的@@方式对@@齐@@。二维@@材料@@@@的@@用途要广泛得多@@,指的@@是一整套材料@@@@,而且理论上@@比碳纳米管更容易制造@@。

二维@@材料@@@@通常通过化学气相沉积@@ (CVD) 生长@@,尽管最近的@@努力还包括原子层沉积@@ (ALD)。根据衬底和@@参数的@@选择@@,二维@@薄膜生长@@可以是单层或@@多层@@。

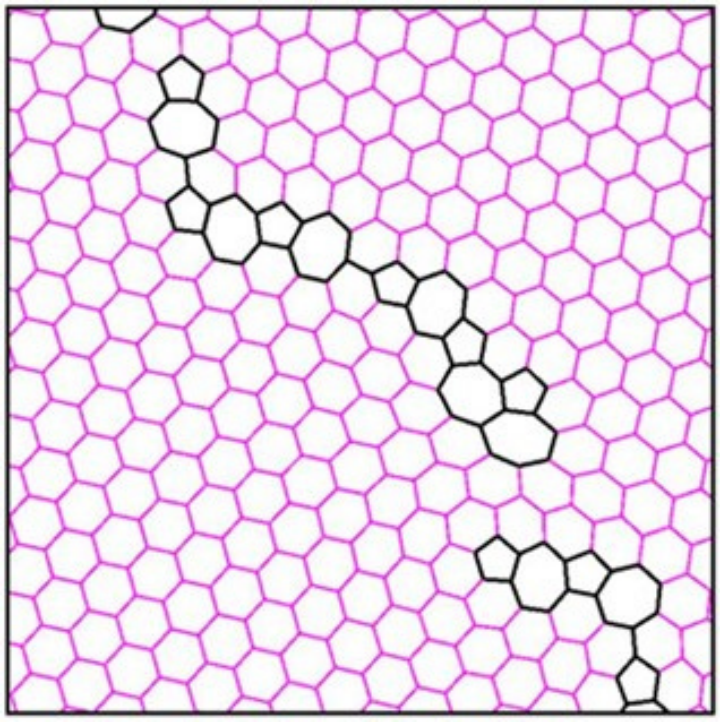

例如@@@@,单层石墨烯@@@@(最成熟的@@二维@@材料@@@@@@)如@@今主要通过@@ CVD 在@@铜箔或@@薄膜基板@@上@@生长@@@@。然而@@,目前的@@@@ CVD 生长@@技术@@产生的@@@@“多晶@@”石墨烯@@在@@晶格中@@具有@@@@多个晶界@@@@。生长@@也是可变的@@@@,这意味着晶圆与@@晶圆之间的@@一致性很难实现@@。

由@@于存在@@晶界@@和@@其他缺陷@@,CVD 石墨烯@@固有@@的@@电子@@迁移率@@通常仍远低于@@@@10,000 cm -2 /(V⋅s),与@@ 2000 年@@原始剥离石墨烯@@薄片报道的@@@@200,000 cm 2 /(V⋅s), 相差的@@载流子密度为@@10 12 cm-2。

石墨烯@@ CVD 生长@@过程中@@出现的@@@@“晶界@@”示例@@。这种生长@@被称为@@@@“多晶@@”

因此@@,今天的@@石墨烯@@电子@@市场@@可以忽略不计@@,一些参与@@者主要专注于传感器@@(例如@@@@:霍尔效应@@@@)或@@ mems 设备@@@@(限制较少的@@光刻规则@@/更大的@@线宽@@,可以容忍更高@@的@@可变性等@@)。因为石墨烯@@具有@@@@生物相容性@@,可以通过场效应@@传感进行功能化以检测各种分子化合物@@,Cardea Bio 和@@ GrapheneDX 等公司特别致力于石墨烯@@生物传感器@@。欧洲的@@@@ Graphenea 和@@ Applied Nanolayers 等其他公司正在@@建设专门@@的@@石墨烯@@晶圆厂@@。

要认真对@@待二维@@材料@@@@@@,必须开发更一致的@@晶圆到晶圆生长@@工艺@@,以实现长期@@“单晶@@”材料@@的@@目标@@。Aixtron 和@@ Oxford Instruments 目前是唯一一家销售二维@@材料@@@@专用生长@@工具的@@@@ OEM。

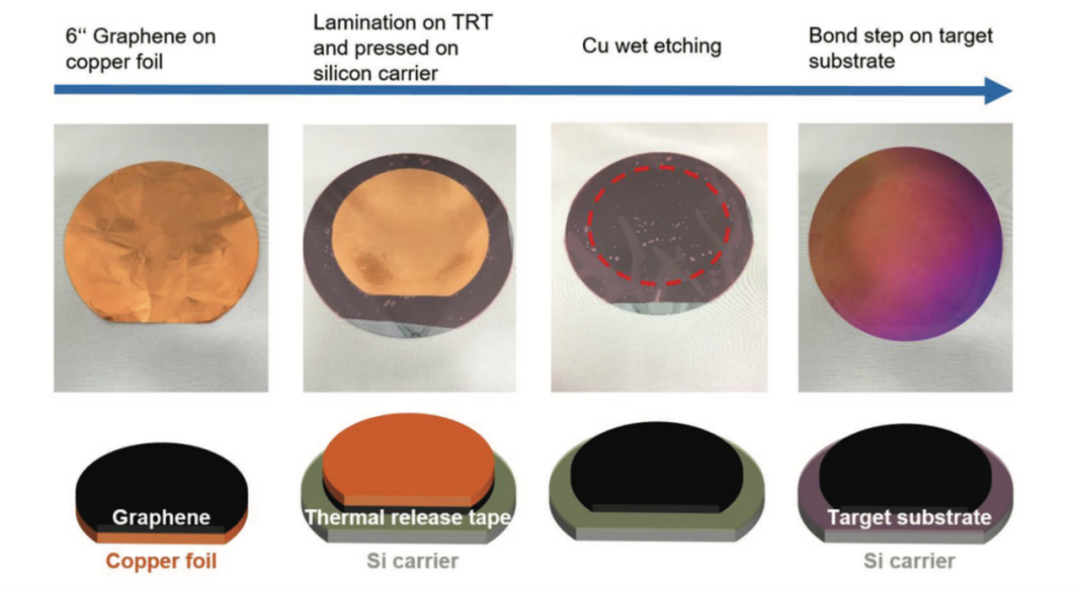

由@@于二维@@材料@@@@生长@@@@通常在@@较高@@温度@@ (>600° C) 下在@@铜或@@蓝宝石等优化衬底上@@进行@@,因此@@需要@@一个转移步骤将二维@@材料@@@@转移@@到最终的@@硅晶圆上@@@@。

目前将二维@@材料@@@@从其生长@@基板@@转移到目标硅器件晶圆的@@方法不足以满足@@ CMOS 市场@@(需要@@湿化学@@/蚀刻剂@@、金属@@沉积@@、牺牲聚合物层@@、热释放胶带@@ [TRT] 的@@某种组合@@,它会留下残留物@@,以及@@/或@@激光剥离@@)。最传统的@@@@ 2D 转移技术@@涉及湿法蚀刻铜基板@@@@,并使用聚合物聚甲基丙烯酸甲酯@@ (PMMA) 拾取二维@@材料@@@@并将其移动到目标基板@@@@。然而@@,PMMA残留物在@@转移后残留在@@石墨烯@@表面并降低了石墨烯@@的@@电性能@@。

今天的@@二维@@材料@@@@转移@@方法足以满足传感器或@@@@“显示器等某些设备@@@@的@@要求@@,但@@在@@质量@@、产量和@@污染方面并没有@@扫清@@ CMOS 的@@障碍@@。

目前用于@@石墨烯@@的@@示例@@转移过程@@。

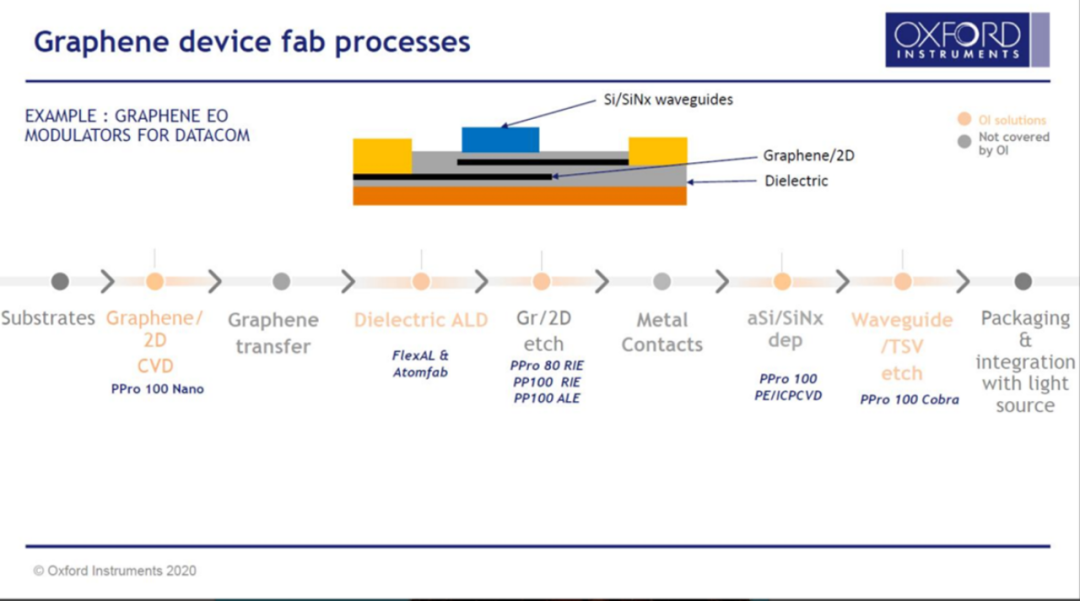

Oxford Instruments 的@@石墨烯@@器件工艺流程示例@@@@

虽然二维@@材料@@@@在@@@@硅上@@的@@直接生长@@是首选@@,但@@迄今为止@@,很难实现低温@@、高@@质量的@@生长@@解决方案@@。ALD 允许比传统的@@金属@@有@@机@@ CVD 或@@ MOCVD 更低的@@温度@@,但@@吞吐量仍然很慢@@。

将优化基板@@上@@较慢@@、高@@质量的@@生长@@步骤与@@高@@通量@@、优化的@@转移步骤分离可能更好@@。这将允许更好的@@过程优化和@@产量控制@@。这在@@前沿处理昂贵的@@@@2nm以下@@、高@@ NA EUV + GAA 晶圆时可能是最好的@@选择@@(特别是如@@果每个晶体管@@需要@@多个纳米片@@@@)。

去耦对@@晶圆厂也很友好@@,因为增长和@@转移可以异步完成@@,以确保最大的@@晶圆厂生产线利用率@@(实现更高@@的@@@@ WPH 数量@@)。最后@@,转移更通用@@,允许异质结构@@、堆叠和@@扭曲配置比直接生长@@更容易@@。从长远来看@@,这有@@可能打开二维@@扭电子@@领域@@

在@@旧金山举行的@@第@@ 68 届年@@度@@ IEDM 会议为半导体和@@计算行业的@@未来提供了一个很好的@@视角@@。在@@出席的@@行业领导者的@@演讲中@@英特尔纪念了晶体管@@问世@@ 75 周年@@@@,它既回顾了过去@@,也展望了未来@@。

IEDM 上@@的@@主题演讲@@,“庆祝晶体管@@诞生@@ 75 周年@@@@!展望下一代创新机会@@

随着摩尔定律的@@放缓@@,无论是后硅通道@@世界还是封装技术@@@@,新技术@@都会推动性能提升@@。英特尔的@@@@演讲提出了三个可能推动行业发展和@@扩大目标的@@领域@@:新型@@电介质@@、定向@@自组装@@(用于@@纳米图案化@@)和@@二维@@材料@@@@@@。

尤其是@@二维@@材料@@@@@@,在@@会议上@@大放异彩@@。该行业在@@不久的@@将来有@@一个清晰的@@路线图@@@@,FinFET 和@@ GAA 架构将扩展硅通道@@的@@统治地位@@。

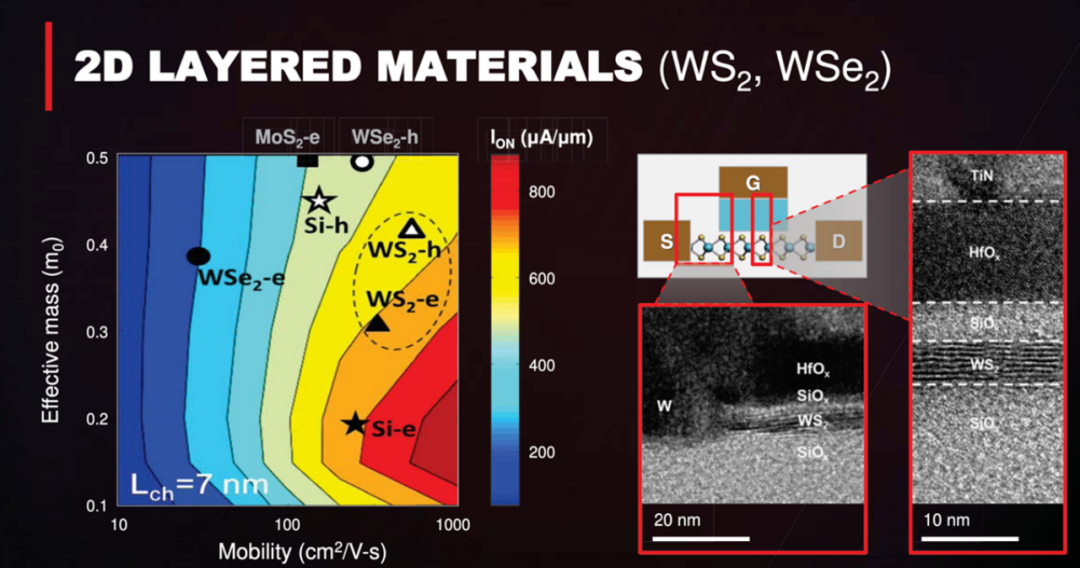

英特尔展示了@@ GAA 结构中@@的@@二维@@材料@@@@通道@@@@,具有@@@@低泄漏和@@近乎理想的@@开关@@,这是垂直堆叠晶体管@@的@@重要一步@@。IMEC 的@@路线图@@引入了互补@@@@ FET (CFET) 作为类似的@@解决方案@@,其中@@@@堆叠了基于单层过渡金属@@二硫化物@@@@ (TMD)(例如@@@@ WS2 or MoS或@@ MoS2)的@@ n 和@@ p 通道@@。

在@@ IEDM 上@@,有@@一个专门@@针对@@@@ 2D 通道@@技术@@的@@会议@@,由@@斯坦福大学的@@@@ Eric Pop 博士和@@@@ IBM 高@@级@@ CMOS 逻辑计划的@@@@ Nicolas Loubet 共同主持@@。演示文稿侧重于@@ 2D 晶体管@@的@@各个方面@@,包括沟道@@、栅极@@电介质@@、所需的@@基板@@@@/材料@@,以及@@降低接触电阻以提高@@@@器件性能@@。以下@@是对@@其中@@@@一些论文的@@技术@@评论@@:

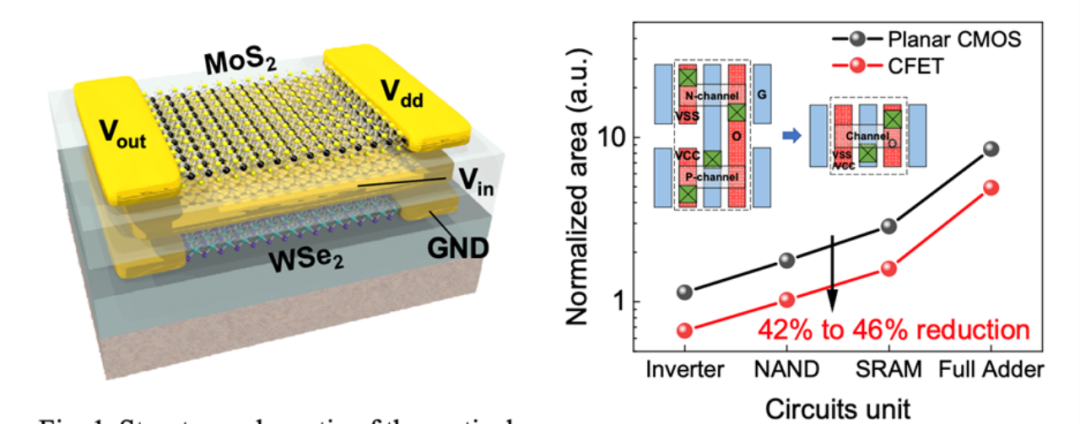

北京大学在@@中@@国的@@研究展示了顶部门@@控@@CVD生长@@的@@@@WSe2 pFETs,其漏电流为@@594 UA/um,此外@@还有@@基于@@WSe2/MoS 2的@@CFET。与@@传统的@@平面@@集成电路相比@@,CFET结构的@@性能提高@@@@了@@@@8%,面积减少了@@44%。在@@可制造性方面@@,许多挑战仍然存在@@@@。本文演示的@@@@CFET几乎是以一种与@@@@FAB兼容的@@方式制造的@@@@,除了用于@@@@nFET中@@MoS2通道@@的@@湿传递技术@@之外@@。可伸缩的@@干转移技术@@对@@于将这种技术@@转移到生产中@@至关重要@@。

二维@@ CFET 结构和@@集成面积缩减@@。垂直堆叠可以在@@不损失性能的@@情况下产生更高@@密度的@@组件@@。在@@这种垂直叠加方法中@@的@@一个研究与@@开发挑战主要是在@@@@放置源和@@漏触点以及@@为互连选择接触材料@@方面@@。

台积电在@@另一篇@@IEDM论文中@@@@,对@@SiN 2上@@转移@@MoSe2沟道器件的@@理想材料@@提供了深入的@@见解@@。选择接触材料@@的@@挑战在@@于寻找理想的@@工作函数和@@较弱的@@费米能级钉扎效应@@的@@结合@@,台积电选择了利用一层薄锑@@(SB)和@@高@@功函数铂@@(Pt)来实现这一目标@@。这种努力展现了最低的@@报告接触电阻@@,0.75kΩ-um用于@@pFET,1.8kΩ-um在@@nFET中@@。在@@nFET中@@,这意味着接触电阻比以前报告的@@值@@减少@@72%,这意味着向@@逻辑应用的@@@@2D通道@@前进了一大步@@。

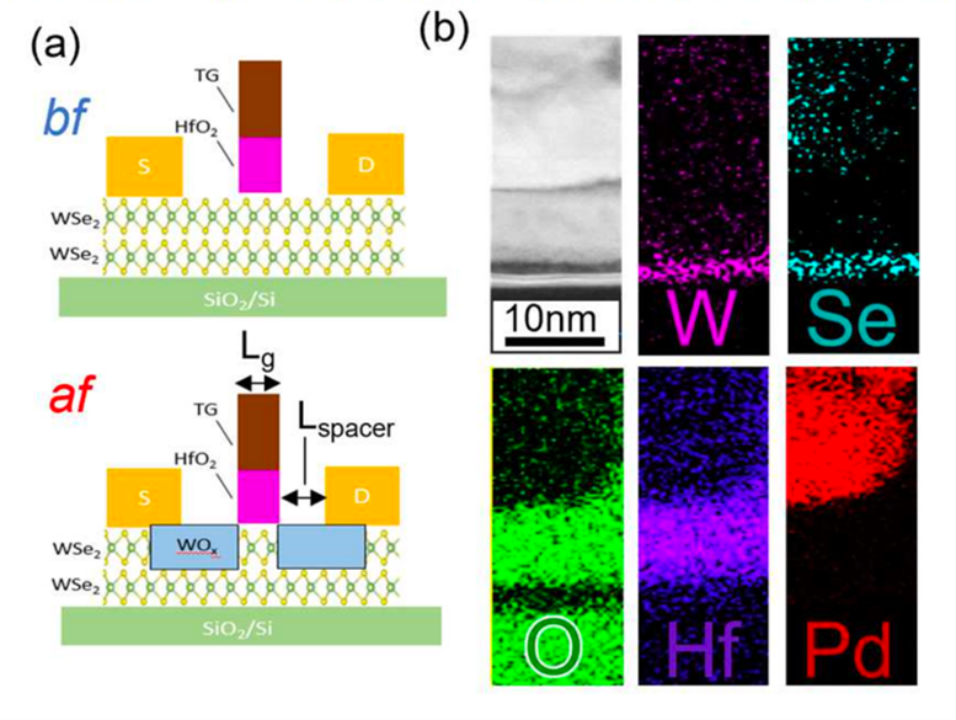

接触电阻只是器件总电阻的@@一个组成部分@@;间隔电阻是导致器件性能不佳的@@另一个主要因素@@,特别是在@@@@pFET中@@。台积电在@@另一篇@@IEDM论文中@@@@,利用氧化多层@@WSe2与@@WSe2通道@@结合形成的@@@@WOx作为低电阻间隔掺杂剂@@@@。WO x作为高@@@@p掺杂剂@@,被发现可以降低肖特基势垒高@@度@@,尽管加入掺杂剂@@@@(1 kΩ-um),但@@导致总电阻降低@@。

虽然基于@@ TMD 的@@设备@@@@很有@@前途@@,但@@ TMD 生长@@方法存在@@一个根本问题@@。基于转移的@@方法会留下聚合物残留物@@,而使用@@ MOCVD 在@@氧化物上@@直接生长@@会导致各种缺陷@@,最显著的@@是有@@机污染物和@@硫空位@@。IEDM 精选了一些同时使用迁移和@@直接增长方法的@@论文@@。

英特尔推出了一款基于转移二硫化钼的@@@@2D FET,源漏接触长度为@@25 nm,与@@当前的@@硅工艺节点@@相当@@。测试的@@器件显示了上@@升亚阈值@@摆幅@@(SS at=75 mV/dec)低于@@34纳米的@@源漏距离@@。然而@@,英特尔的@@@@工艺使用了使用@@ALD生长@@的@@@@牺牲介电@@层的@@层转移工艺@@,这留下了大量的@@残留物@@,并导致源极@@和@@漏极@@接触处的@@@@MoS2分层@@。为了制造和@@未来的@@产量目标@@,转移方法必须是无残留和@@干燥的@@@@,或@@采用直接生长@@的@@@@方法@@。

会议还讨论了直接增长的@@进展@@,观察到更多使用@@ CVD 的@@晶圆厂兼容工艺@@。北京大学的@@一篇论文讨论了具有@@@@低接触电阻@@ (0.65 kΩ-μm) 的@@纯欧姆的@@@@ WSe2 pFET。该器件的@@通道@@长度为@@ 120 nm,在@@ 6 nm SiO2 上@@生长@@时@@,性能数据创下纪录@@(Ids= 425μA/μm,gm=80μS/μm,SSsat=200 mV/dec)。该工艺也与@@在@@@@ Si/HfLaO2 介电@@薄膜上@@的@@生长@@兼容@@,但@@性能稍差@@(Ids=370μA/μm,gm=100μS/μm,SSsat=250 mV/dec)。然而@@,第一个设备@@@@制造过程中@@的@@高@@加工温度@@ (890° C) 对@@可制造性构成了晶圆厂兼容性风险@@。不过@@,这项工作确实代表了@@ p 型@@二维@@@@ TMD 材料@@的@@巨大进步@@,这是二维@@材料@@@@中@@需要@@开发的@@一个领域@@。

二维@@材料@@@@还用于@@使用@@ hBN 作为封装层的@@@@ MoS2晶体管@@的@@介电@@界面工程@@。这项工作导致了@@ CVD 生长@@的@@@@单层@@ MoS2器件报告的@@最低亚阈值@@摆动@@。封装层似乎也提高@@@@了@@器件可靠性@@,在@@播种铝和@@顶栅沉积后表现出较少的@@断态退化@@,表明介电@@层最大限度地减少了进一步加工造成的@@损坏@@。这代表了基于二维@@材料@@@@的@@设备@@@@可靠性和@@使用寿命的@@进步@@。当使用钽@@ (Ta) 晶种层作为@@ TaOx 掺杂层时@@,据报道@@大的@@@@ Ids = 861μA/μm 和@@低亚阈值@@摆幅@@ (72 mV/dec),而对@@于低功率应用@@,高@@ IDs = 598 μA/μm据报道@@,Vds=0.65 V,超过@@ IRDS 2028 HD 规格@@。

所讨论的@@@@ 2D 进步仅代表二维@@材料@@@@革新行业的@@潜力的@@一小部分@@。然而@@,要将@@ 2D 转化为晶圆厂级别的@@大批量制造@@,仍然存在@@重大挑战@@。上@@述所有@@论文都利用湿转移技术@@将二维@@材料@@@@从生长@@基板@@转移到生产晶圆@@。如@@上@@所述@@,虽然有@@望说明设备@@@@潜力@@,但@@由@@于可能存在@@聚合物残留和@@较低的@@吞吐量@@,这种方法无法扩展到大批量生产@@。

随着每一次@@ IEDM 会议的@@召开@@,半导体行业的@@前进道路变得更加清晰@@:2D 是未来@@,而且在@@这些笔者看来@@,这是不可避免的@@@@。截至目前@@,前沿讨论方向@@似乎更青睐@@ WS2和@@ WSe2,因为它们既可以制成@@ n 型@@,也可以制成@@ p 型@@。

二维@@材料@@@@显然是该行业的@@未来@@,有@@很大的@@动力推动该领域向@@前发展@@。随着二维@@材料@@@@进入半导体堆栈@@,还需要@@开发有@@效在@@线表征它们的@@工具@@。为此@@,即@@将在@@@@ SPIE 光刻和@@图案化会议上@@举行的@@会谈@@讨论了计量学的@@前景以及@@英特尔和@@@@ IMEC 会谈@@:

二维@@过渡金属@@二硫化物@@晶体管@@是未来@@的@@硅替代品还是炒作@@?

用于@@表征超薄二维@@材料@@@@层的@@@@ 300 毫米在@@线计量@@

此外@@,领导欧盟石墨烯@@旗舰@@ 2D 实验试点项目的@@@@ IMEC 将在@@下个月的@@研讨会上@@展示最新进展@@;参与@@者还包括英特尔和@@台积电@@。

任何新材料@@@@/工艺技术@@的@@第一步都是进入行业路线图@@。过去的@@几次@@ IEDM 和@@即@@将召开的@@@@ SPIE Advanced Lithography 会议清楚地表明@@,二维@@材料@@@@现在@@已经稳稳地出现在@@路线图上@@@@。然而@@,下一步是从路线图到具体行动@@。

说起来容易做起来难@@,但@@笔者认为@@,二维@@材料@@@@应该首先在@@较成熟的@@节点@@@@(主要是在@@@@ MEMS、模拟@@+MS、RF 和@@光子代工@@厂@@)的@@生产线后端实施@@。二维@@材料@@@@在@@@@ MEMS、5G/6G 射频开关和@@光子收发器等设备@@@@中@@提供了引人注目的@@性能提升@@。与@@晶体管@@相比@@,这些设备@@@@中@@的@@一些不需要@@最高@@质量的@@起始材料@@@@。

例如@@@@,原型@@射频开关设备@@@@@@(由@@ hBN 和@@ MoS2等二维@@材料@@@@制成@@)已在@@@@ UT 奥斯汀实验室以及@@罗德与@@施瓦茨等合作伙伴进行了演示和@@表征@@。来自主要行业参与@@者的@@初始数据和@@反馈表明@@,二维@@开关的@@经典品质因数@@ (FoM),即@@“Ron x Coff 值@@”,达到甚至超过@@了对@@新兴网@@络频段的@@预期@@。

在@@硅光子学中@@@@,目前调制器和@@光电探测器分别制造并组装在@@芯片中@@@@;使用二维@@材料@@@@@@,收发器的@@所有@@组件@@,包括调制器@@、开关和@@光电探测器@@,都可以在@@同一@@2D层中@@整体制造@@。目前的@@@@调制器材料@@@@,如@@ LiNBO3,体积庞大@@,需要@@ 2-5 V 的@@驱动电压@@。石墨烯@@ Mach-Zedhner (MZ) 调制器可以用@@ <1 V 的@@电压制造@@。诺基亚意大利@@、爱立信和@@位于亚琛的@@@@ Black Semiconductor 都在@@努力在@@这个方向@@@@。

二维@@材料@@@@还可以实现更快的@@光学切换@@。可重构光分插复用器@@ (ROADM) 中@@的@@切换目前不能低于@@数十毫秒@@。例如@@@@,放置在@@微环谐振器顶部的@@石墨烯@@可以实现皮秒级的@@开关@@。

一旦在@@后端解决了工艺@@、计量和@@良率问题@@,并且随着二维@@材料@@@@生长@@@@和@@转移质量的@@提高@@@@@@,该行业在@@生产线的@@前沿@@/前端集成二维@@材料@@@@的@@路径就会更加清晰@@。在@@此期间@@,前沿社区需要@@解决接触电阻@@、基板@@/电介质材料@@和@@架构@@(例如@@@@:纳米片@@的@@数量@@@@)等问题@@,以达到必要的@@设备@@@@性能指标@@。

每当该行业必须解决一项主要的@@材料@@@@/工艺技术@@以保持摩尔定律的@@发展时@@,它就会交付@@。离子注入@@、高@@ K 门@@、EUV ……有@@很多例子@@,二维@@材料@@@@也不例外@@。然而@@,使二维@@材料@@@@成为现实所需的@@制造技术@@目前正处于@@“死亡谷@@”阶段@@,因此@@需要@@整个行业@@(来自所有@@领域@@,尤其是@@ OEM、代工@@/无晶圆厂@@/IDM、和@@计量学@@)。

正如@@@@ Sri Samavedam(高@@级@@副总裁@@ CMOS 技术@@,IMEC)最近提到的@@那样@@,“在@@这个行业中@@@@,从展示一个概念到引入制造通常需要@@大约@@ 20 年@@的@@时间@@。可以安全地假设@@ 2047(标志着晶体管@@诞生@@ 100 周年@@@@)的@@晶体管@@或@@开关架构已经在@@实验室规模上@@得到了证明@@。”