本文转载自@@: 硬件十万个为什么微信公众号@@@@

电容@@在@@高速@@@@ PCB 设计@@中@@起着重要的作用@@,通常也是@@ PCB 上用得最多的器件@@。在@@ PCB 中@@,电容@@通@@ 常分为滤波电容@@@@@@、去耦电容@@@@、储能电容@@@@等@@@@。

1、 电源输出电容@@@@,滤波电容@@@@

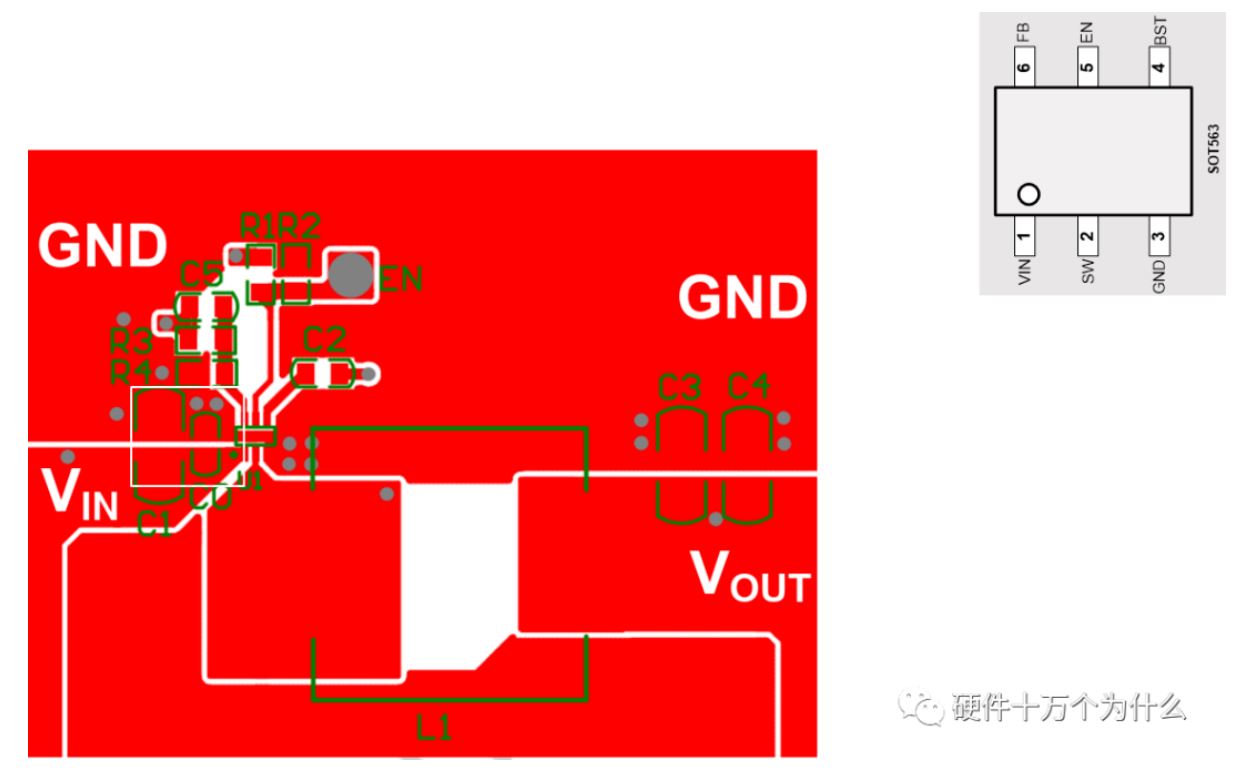

我们通常把电源模块输入@@、输出回路的电容@@称为滤波电容@@@@@@。简单理解就是@@,保证输入@@、输出电源@@ 稳定的电容@@@@。在@@电源模块中@@@@,滤波电容@@@@摆放的原则是@@“先大@@后小@@”。如@@图@@@@2.48.1所示@@,滤波电容@@@@按箭头@@ 方向先大@@后小@@摆放@@。

电源设计@@时@@,要注意走线和@@铜皮足够宽@@、过孔数量足够多@@,保证通流能力满足需求@@。宽度和@@过孔@@ 数量结合电流大@@小来评估@@。

电源输入电容@@@@

电源输入电容@@@@与开关环路形成一个电流环@@。这个电流环路的变化幅度大@@@@,Iout的幅度@@。频率是开关频率@@。DCDC芯片开关过程中@@产生@@,这个电流环产生的电流的变化@@,包含了较快的@@di/dt。

同步@@BUCK的方式@@,续流路径要经过芯片的@@GND管脚@@,输入电容@@要接在@@芯片的@@GND和@@Vin之间@@,路径竟可能的短粗@@。

这个电流环面积足够的小@@,这个电流环对外辐射就会越好@@。

2、 去耦电容@@@@

高速@@ IC的电源引脚需要足够多的去耦电容@@@@@@,最好能保证每个引脚有一个@@。实际设计@@中@@@@,如@@果没@@ 有空间@@摆放去耦电容@@@@@@,则可以酌情删减@@。

IC 电源引脚的去耦电容@@@@的容值通常会比较小@@,如@@ 0.1μF、0.01μF 等@@;对应的封装@@也比较小@@,如@@ 0402封装@@、0603封装@@等@@@@。在@@摆放去耦电容@@@@时@@,应注意以下几点@@。

(1)尽可能靠近电源引脚放置@@,否则可能起不到去耦作用@@。理论上讲@@,电容@@有一定的去耦半径范@@ 围@@,所以应严格执行就近原则@@。

(2)去耦电容@@@@到电源引脚引线尽量短@@,而且引线要加粗@@@@,通常线宽为@@8~15mil(1mil = 0.0254mm)。加粗@@目的在@@于减小引线电感@@,保证电源性能@@。

(3)去耦电容@@@@的电源@@、地引脚从焊盘引出线后@@,就近打孔@@,连接到电源@@、地平面上@@。该引线同样要@@ 加粗@@,过孔尽量用大@@孔@@,如@@能用孔径@@10mil 的孔@@,就不用@@8mil的孔@@。

(4)保证去耦环路尽量小@@。去耦电容@@@@常见的@@摆放示例如@@图@@@@@@2.48.2~图@@2.48.4所示@@。图@@2.48.2~图@@2.48.4所示@@是@@SOP封装@@的@@IC 去耦电容@@@@的摆放方式@@,QFP等@@封装@@的@@与此类似@@。

常见的@@ BGA封装@@,其去耦电容@@@@通常放在@@@@ BGA下面@@,即背面@@。由于@@ BGA 封装@@引脚密度大@@@@,因此去@@ 耦电容@@一般放的不是很多@@,但应尽量多摆放一些@@,如@@图@@@@2.48.5所示@@。

3、储能电容@@@@

储能电容@@@@的作用就是保证@@IC在@@用电时@@,能在@@最短的时间内提供电能@@。储能电容@@@@的容值一般比较@@ 大@@,对应的封装@@也比较大@@@@。在@@PCB中@@,储能电容@@@@可以离器件远一些@@,但也不能太远@@,如@@图@@@@2.48.6所示@@。常见的@@储能电容@@@@扇孔@@方式@@,如@@图@@@@2.48.7所示@@。

电容@@扇孔@@、扇线原则如@@下@@。

(1)引线尽量短且加粗@@@@,这样有较小的寄生电感@@。

(2)对于储能电容@@@@@@,或@@者过电流比较大@@的器件@@,打孔时应尽量多打几个@@。

(3)当然@@,电气性能最好的扇孔是盘中@@孔@@。实际需要综合考虑@@