半导体@@制作工艺@@可分为前端和后端@@:前端主要是晶圆制作和光刻@@(在晶圆上绘制电路@@);后端主要是芯片的封装@@。随着前端工艺@@微细化技术@@逐渐达到极限@@,后端工艺@@的重要性愈发突显@@。作为可以创造新附加价值的核心突破点@@,其技术@@正备@@受瞩目@@。

此系列文章将以@@《提高@@半导体@@附加价值的封装与测试@@@@》一书内容为基础@@,详细讲解后端工艺@@@@。

#1 半导体@@后端工艺@@@@

制作半导体@@产品的第一步@@,就是根据所需功能设计芯片@@(Chip)。然后@@,再将芯片制作成晶圆@@(Wafer)。由于晶圆由芯片反复排列而成@@,当我们细看已完成的晶圆时@@,可以看到上面有很多小格子状的结构@@,其中@@一个小格子就相当于一个芯片@@。芯片体积越大@@,每个晶圆可产出的芯片数量就越少@@,反之亦然@@。

半导体@@设计不属于制程工序@@,半导体@@产品的制程工序大体可分为晶圆制作@@、封装和测试@@@@。其中@@,晶圆制作属于前端@@(Front End)工艺@@;封装和测试@@@@属于后端@@(Back End)工艺@@。晶圆的制作工艺@@中也会细分前端和后端@@,通常是@@CMOS制程工序属于前端@@,而其后的金属布线工序属于后端@@。

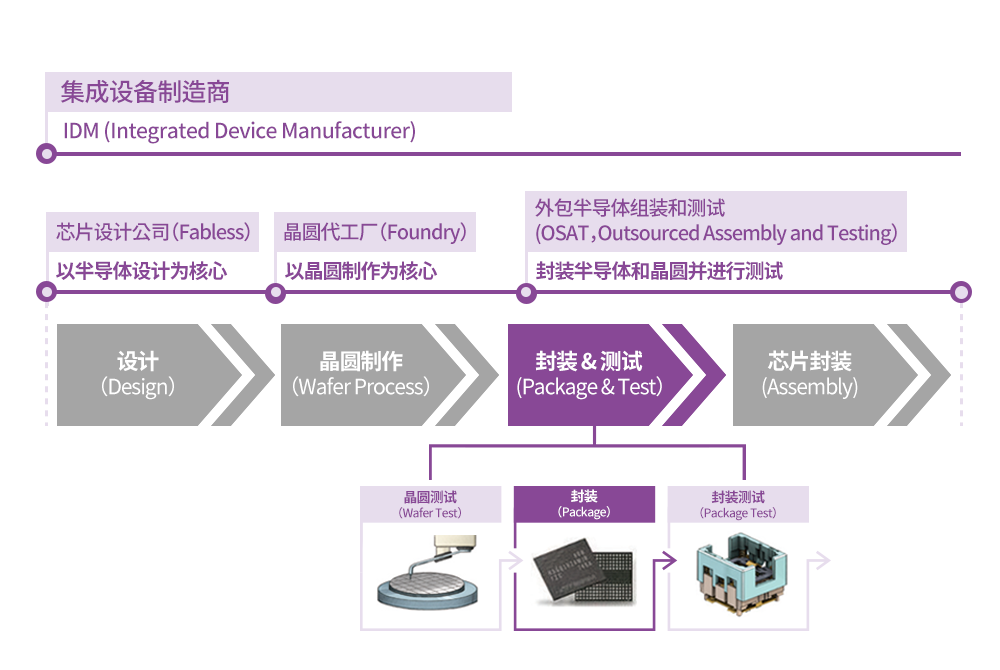

图@@1:半导体@@制作流程与半导体@@行业划分@@(ⓒHANOL出版社@@/photograph.SENSATA)

图@@1展示了@@半导体@@制程工艺@@及其行业的划分@@。只从事半导体@@设计的产业运作模式被称作芯片设计公司@@(Fabless),该模式的典型代表@@有高通@@(Qualcomm)、苹果@@(Apple)等@@。负责晶圆制作的制造商被称为晶圆代工厂@@(Foundry),他们根据@@Fabless公司的设计制作晶圆@@,其中@@最典型的代表@@要台积电@@(TSMC)了@@,DB HiTek、Magnachip等@@韩企也采用这一模式@@。经@@Fabless设计和@@Foundry制造的晶圆还需经@@过封装和测试@@@@@@,专门负责这两道工艺@@的企业就是外包半导体@@组装@@和测试@@@@(OSAT,Outsourced Assembly and Testing),其典型代表@@有@@ASE、JCET、星科金朋@@(Stats Chippac)、安靠@@(Amkor)等@@。此外@@,还有像@@SK海力士这样集半导体@@设计@@、晶圆制造@@、封装和测试@@@@等@@多个产业链环节于一身的集成设备@@制造商@@(IDM,Integrated Device Manufacturer)。

如图@@@@1所示@@,封装和测试@@@@工艺@@的第一步就是晶圆测试@@@@@@。封装后@@,再对封装进行测试@@@@。

半导体@@测试@@@@的主要目的之一就是防止不良产品出厂@@。一旦向客户提供@@不良产品@@,客户对我们的信任就会大打折扣@@,进而导致公司销售业绩的下降@@,还会引发赔偿等@@资金上的损失@@。因此@@,我们必须在产品出厂前对其进行细致的全面检测@@@@。半导体@@测试@@@@须根据产品的各种特性@@,对其各参数进行测试@@@@,以确保产品的品质和可靠度@@。当然@@,这需要时间@@、设备@@和劳动力上的投入@@,产品的制造成本也会随之增加@@。因此@@,众多测试@@工程师正致力于减少测试@@时间和测试@@参数@@。

#2 测试@@的种类@@

表@@1: 测试@@分类@@(ⓒ HANOL出版社@@)

测试@@工艺@@可依据不同的测试@@对象@@,分为晶圆测试@@@@和封装测试@@@@@@;也可根据不同的测试@@参数@@,分为温度@@、速度和运作模式测试@@等@@三种类型@@(见表@@@@1)。

温度测试@@以施加在试验样品上的温度为标准@@:在高温测试@@中@@,对产品施加的温度比产品规格@@@@1 所示@@温度范围的上限高出@@10%;在低温测试@@中@@,施加温度比规格@@下限低@@10%;而恒温测试@@的施加温度一般为@@25℃。在实际使用中@@,半导体@@产品要在各种不同的环境中运作@@,因此@@必须测试@@产品在不同温度下的运作情况以及其温度裕度@@(Temperature Margin)。以半导体@@存储器为例@@,高温测试@@范围通常为@@85~90℃,低温测试@@范围为@@-5~-40℃。

1 规格@@(Spec): specification的缩写@@,指产品配置@@,即制造产品时在设计@@、制作方法上或@@对所需特性的各种规定@@。

速度测试@@又分为核心@@(Core)测试@@和速率测试@@@@。核心测试@@主要测试@@试验样品的核心运作@@,即是否能顺利实现原计划的目标功能@@。以半导体@@存储器为例@@,由于其主要功能是信息的存储@@,测试@@的重点便是有关信息存储单元@@@@的各项参数@@。速率测试@@则是测量样品的运作速率@@,验证产品是否能按照目标速度运作@@。随着对高速运转半导体@@产品需求的增加@@,速率测试@@目前正变得越来越重要@@。

运作模式测试@@细分为直流测试@@@@(DC Test)、交流测试@@@@(AC Test)和功能测试@@@@(Function Test):直流测试@@验证直流电流和电压参数@@;交流测试@@@@(AC Test)验证交流电流的规格@@@@,包括产品的输入和输出转换时间等@@运作特性@@;功能测试@@则验证其逻辑功能是否正确运作@@。以半导体@@存储器为例@@,功能测试@@就是指测试@@存储单元@@@@@@(Memory cell)与存储器周围电路逻辑功能是否能正常运作@@。

#3 晶圆测试@@@@

晶圆测试@@@@的对象是晶圆@@,而晶圆由许多芯片组成@@@@,测试@@的目的便是检验这些芯片的特性@@和品质@@。为此@@,晶圆测试@@@@需要连接测试@@机和芯片@@,并向芯片施加电流和信号@@。

完成封装的产品会形成像锡球@@(Solder Ball)一样的引脚@@(Pin),利用这些引脚可以轻而易举完成与测试@@机的电气连接@@。但在晶圆状态下@@,连接两者就需要采取一些特殊的方法@@,比如探针@@卡@@(Probe Card)。

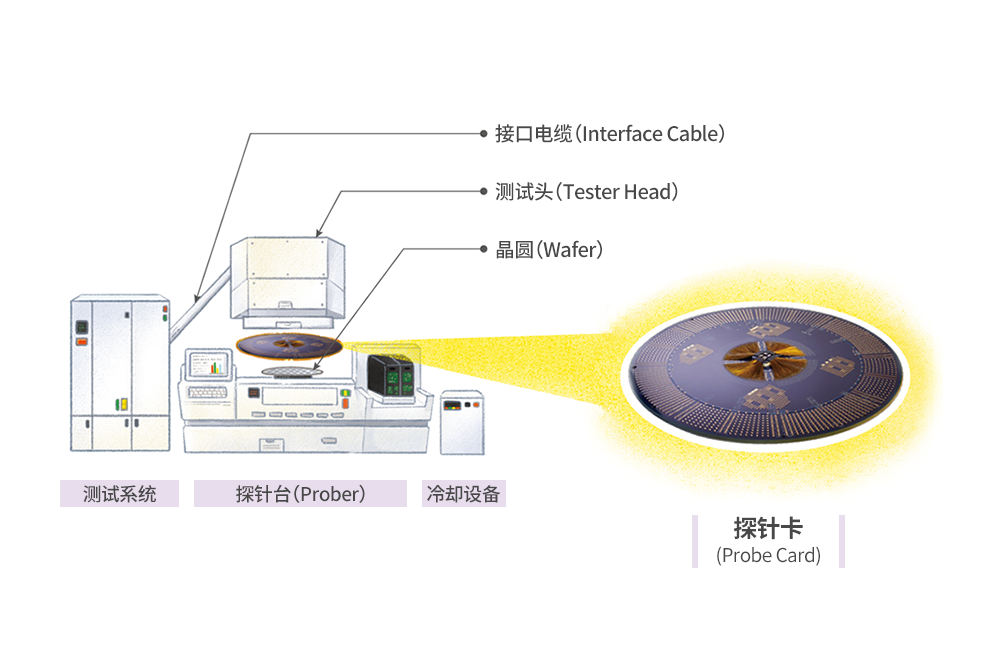

如图@@@@2所示@@,探针@@卡是被测晶圆和测试@@机的接口@@,卡上有很多探针@@@@2可以将测试@@机通讯接口和晶圆的焊盘直接连接起来@@,卡内还布置了@@很多连接探针@@与测试@@机的连接线材@@。探针@@卡固定在测试@@头上@@,晶圆探针@@台通过使探针@@卡与晶圆焊盘点精准接触@@,完成测试@@@@。

2 探针@@: 与晶圆焊盘进行电气连接和直接接触的针状物@@。

图@@2 : 晶圆测试@@@@系统模式图@@@@(ⓒ HANOL出版社@@/photograph.Formfactor)

将晶圆正面朝上装载后@@,再把图@@@@2右侧的探针@@卡反过来使针尖朝下@@,实现与晶圆焊盘的准确对位@@。这时@@,温度调节设备@@根据测试@@所需温度条件@@,施加相应温度@@。测试@@系统通过探针@@卡传送电流和信号@@,并导出芯片讯号@@,从而读取测试@@结果@@。

探针@@卡要根据被测芯片的焊盘布局和晶圆芯片排布制作@@,即探针@@与被测晶圆焊盘布局要一致@@。而且@@,要按照芯片排列@@,反复排布探针@@@@。其实@@,在实际操作中@@,仅凭一次@@接触是无法测试@@晶圆的所有芯片的@@。因此@@,在实际量产过程中要反复接触@@2~3次@@。

一般来讲@@,晶圆测试@@@@依次@@按照@@“电气参数监控@@(EPM) → 晶圆老化@@@@(Wafer Burn in) → 测试@@ → 维修@@(Repair) → 测试@@”顺序进行@@。下面@@,我们来详细讲解一下晶圆测试@@@@的具体工序@@。

◎ 电气参数监控@@(EPM,Electrical Parameter Monitoring)

测试@@可以筛选出不良产品@@,又可以反馈正在研发或@@量产中的产品缺陷@@,从而进行改善@@。相比而言@@,电气参数监控@@的主要目的是后者@@,即通过评价分析产品单位@@@@188足彩外围@@app

的电气特性@@,对晶圆的制作工序提供@@反馈@@。具体来说@@,就是在进入正式晶圆测试@@@@前@@,采用电学方法测量晶体管的特性@@和接触电阻@@,验证被测产品是否满足设计和@@@@188足彩外围@@app

部门提出的基本特性@@。从测试@@的角度来看@@,就是利用@@188足彩外围@@app

的电学性能提取直流参数@@(Parameter),并监控各单位@@@@188足彩外围@@app

的特性@@。

◎ 晶圆老化@@@@(Wafer Burn in)

图@@3:产品使用时间与不良率@@(ⓒ HANOL出版社@@)

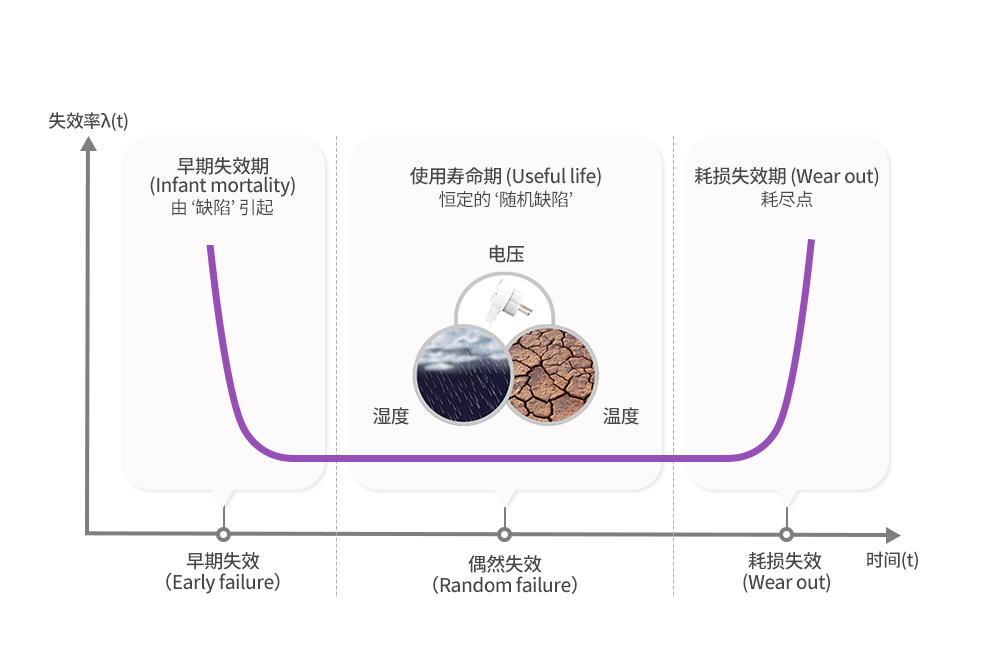

图@@3以时间函数揭示了@@产品生命周期@@中的不良率@@ [曲线呈现出如同浴缸的形状@@,故被称作浴盆曲线@@(Bath-Tub Curve)] :早期@@失效@@(Early failure)期@@,产品因制作过程中的缺陷所导致的失效率较高@@;制造上的缺陷消失后@@,产品进入偶然失效@@(Random failure)期@@,在此期@@间@@,产品的失效率降低@@;产品老化@@磨损后进入耗损@@(Wear out)失效期@@@@,失效率明显再次@@上升@@。可见@@,如果完成产品后立即提供@@给客户@@,早期@@失效@@会增加客户的不满@@,造成退货等@@产品问题的可能性也很大@@。

“老化@@(Burn in)”的目的就是为识别产品的潜在缺陷@@,提前发现产品的早期@@失效@@状况@@。晶圆老化@@@@是在晶圆产品上施加温度@@、电压等@@外界刺激@@,剔除可能发生早期@@失效@@的产品的过程@@。

◎ 晶圆测试@@@@

在晶圆老化@@@@@@(Wafer Burn in)测试@@剔除早期@@失效@@产品后使用探针@@卡进行晶圆测试@@@@@@。晶圆测试@@@@是在晶圆上测试@@芯片电学性能的工序@@。其主要目的包括@@:提前筛选出不良芯片@@、事先剔除封装@@/组装@@3过程中可能产生的不良产品并分析其原因@@、提供@@工序反馈信息@@,以及通过晶圆级验证@@(Wafer Level Verification)提供@@188足彩外围@@app

与设计上的反馈等@@@@。

在晶圆测试@@@@中筛选出的部分不良单元@@@@4,将会在我们下面@@要讲到的维修@@@@(Repair)过程中被备@@用单元@@@@(Redundancy cell)替换@@。为测试@@这些备@@用单元@@是否能正常工作@@,以及芯片能否成为符合规格@@的良品@@,在维修@@工序后@@,必须重新进行一次@@晶圆测试@@@@@@。

3 组装@@ : 与基板或@@系统实现电气或@@直接连接@@、组装@@的工序@@;

4单元@@(Cell): 为在记忆@@188足彩外围@@app

存储信息@@(Data)所需的最小单位@@的单元@@数组@@;DRAM存储单元@@@@(Cell)由一个晶体管@@(Transistor)和一个电容器@@(Capacitor)组成@@;

◎ 维修@@(Repair)

维修@@作为内存半导体@@测试@@@@中的一道工序@@,是通过维修@@算法@@(Repair Algorithm),以备@@用单元@@取代不良单元@@的过程@@。假设在晶圆测试@@@@中发现@@DRAM 256bit内存的其中@@@@1bit为不良@@,该产品就成了@@@@255bit的内存@@。但如果经@@维修@@工序@@,用备@@用单元@@替换@@不良单元@@@@,255bit的内存@@就又重新成了@@@@256bit的内存@@,可以向消费者正常销售@@。可见@@,维修@@工序可以提高@@产品的良率@@,因此@@,在设计半导体@@存储器时@@,会考虑备@@用单元@@的制作@@,并根据测试@@结果以备@@用单元@@取代不良单元@@@@。当然@@,制作备@@用单元@@就意味着要消耗更多的空间@@@@,这就需要加大芯片的面积@@。因此@@,我们不可能制作可以取代所有不良内存的充足的备@@用@@单元@@@@(比如可以取代所有@@256bit的备@@用@@256bit等@@)。要综合考虑工艺@@能力@@,选择可以最大程度地提升良率的数量@@。如果工艺@@能力强@@,不良率少@@,便可以少做备@@用单元@@@@,反之则需要多做@@。

维修@@可分为列@@(Column)单位@@和行@@(Row)单位@@:备@@用列取代不良单元@@所在的列@@;备@@用行取代不良单元@@所在的行@@。

DRAM的维修@@要先切断不良单元@@的列或@@行@@,再连接备@@用列或@@行@@。维修@@可分为激光维修@@@@和电子@@保险丝@@(e-Fuse)维修@@。激光维修@@@@,顾名思义@@,就是用激光烧断与不良单元@@的连接@@。这要求先脱去晶圆焊盘周围连线的保护层@@(Passivation layer),使连接线裸露出来@@。由于完成封装后@@的芯片表@@面会被各种封装材料所包裹@@,激光维修@@@@方法只能用于晶圆测试@@@@@@。电子@@保险丝维修@@则采用在连接线施加高电压或@@电流的方式断开不良单元@@@@。这种方法与激光维修@@@@不同@@,它通过内部电路来完成维修@@@@,不需要脱去芯片的保护膜@@。因此@@,除晶圆测试@@@@外@@,该方法在封装测试@@@@中也可使用@@。

#4 封装测试@@@@

在晶圆测试@@@@中被判定为良品的芯片@@,经@@封装工序后需要再进行封装测试@@@@@@,因为这些芯片在封装工序中有可能发生问题@@。而且@@,晶圆测试@@@@同时测试@@多个芯片@@,测试@@设备@@性能上的限制可能导致其无法充分测试@@目标参数@@。与此相反@@,封装测试@@@@以封装为单位@@进行测试@@@@,对测试@@设备@@的负荷相对较小@@,可以充分测试@@目标参数@@,从而选出符合规格@@的良品@@。

封装测试@@@@方法如图@@@@@@4所示@@:先把@@“03”的封装引脚@@(Pin,图@@中为锡球@@)朝下装入封装测试@@@@插座内@@,使引脚与插座内的引脚对齐@@,然后@@再将封装测试@@@@插座固定到封装测试@@@@板@@(Package Test Board)上进行测试@@@@。

图@@4:封装测试@@@@系统@@(ⓒHANOL出版社@@/ photograph.NST, SENSATA)

◎ 老化@@测试@@@@(Test During Burn In,TDBI)

前边也提到过@@,“老化@@(Burn in)”是为了@@提前发现产品的早期@@失效@@@@,向晶圆产品施加温度@@、电压等@@外界刺激@@的工序@@。这一工序既可在晶圆测试@@@@中进行@@,也可在封装测试@@@@阶段进行@@。封装后@@实施的@@“老化@@”被称为老化@@测试@@@@@@(TDBI)。大部分半导体@@产品在晶圆和封装测试@@@@均进行老化@@测试@@@@@@,以便更加全面地把握产品的特性@@@@,寻找缩减老化@@时间和工序数量的条件@@。可见@@,老化@@对于量产来说是一道最有效的工序@@。

◎ 测试@@

这是验证数据手册@@@@5中定义的运作模式在用户环境中能否正常工作的流程@@。通过温度测试@@@@,检验产品交流@@/直流参数的缺陷@@,以及单元@@@@&外围电路@@(Cell & Peri)区域的运作是否满足客户要求的规格@@@@。此时@@,需要在比数据手册@@中规定的条件更为恶劣的条件下@@,甚至是最糟糕的条件下进行测试@@@@。

5 数据手册@@(Data Sheet):定义半导体@@产品基本配置与特性等@@具体信息的文件@@。

◎ 外观@@(Visual)检测@@

完成所有测试@@后@@,需通过激光打标@@(Laser Marking)把测试@@结果和速率特性@@(尤其是需要区分速率时@@)记录在产品封装的表@@面@@。经@@封装测试@@@@和激光打标后@@,将良品装入封装托盘@@(Tray),产品即可出厂了@@@@。当然@@,在出厂前@@,还要进行最后一道测试@@@@——外观@@测试@@@@,以剔除外观@@上的缺陷@@。外观@@检测@@主要查看是否有龟裂@@、打标错误@@、装入错误的托盘等@@问题@@;锡球方面主要检查球是否被压扁@@,或@@球是否脱落等@@问题@@。

本文转载自@@:SK海力士微信公众号@@@@