作者@@: 谢敏钊@@,来源@@: 韬略科技@@EMC微信公众号@@

一@@. 前言@@

随着科技和智能设备@@的飞速发展@@,越来越多的电子@@产品应运而生@@,但随之而来的电磁辐射问题也越来越多@@,电磁辐射污染@@问题成为了继大气污染@@@@、水污染@@及噪声污染@@之后@@的第四@@大污染@@@@,复杂的电磁环境不仅容易在电子@@产品间相互影响@@,严重的还会影响到我们的生活质量以及我们的身心健康@@。而时钟问题作为@@EMC测试中最常见的辐射问题之一@@@@,对工程师的困扰也十分严重@@,而铺地接地作为硬件工程师@@LAYOUT基本技能之一@@@@,也蕴藏的很多学问在里面@@,稍有不慎@@,就可能导致@@EMC辐射超标@@,本文则针对该问题结合实际情况进行探讨@@。

二@@. 实际案例@@

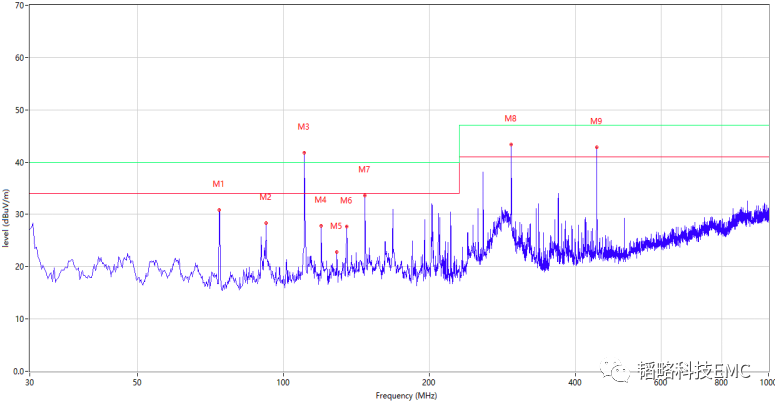

本文的主角是一@@款后@@装车机@@,经过测试摸底确认为时钟辐射超标@@@@,具体数据如下@@:

经过频谱仪和时钟筛查后@@@@,最终锁定在某个模块的时钟上@@,如下图@@:

(可以借助频谱仪锁定具体问题点@@)

三@@. 整改过程@@

具体问题源头锁定后@@@@,开始进行下一@@步的整改@@,采用常规的电阻@@、磁珠@@、电容滤波效果都不佳后@@@@,那就要继续往其他的角度去思考是不是某个模块或@@者线路或@@者地设计有问题导致@@,滤波基本都没有效果@@。

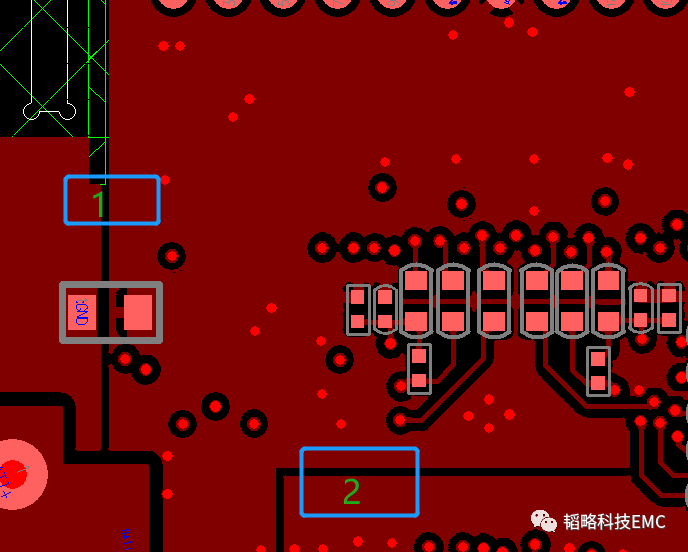

继续用频谱仪点板上的地@@,发现时钟接受端模块的地@@(模拟地@@)有超标频点的时钟出现@@,比底噪高出十几个@@dB,而用探针点系统地却没有超标时钟出现@@,说明模拟地@@被时钟@@“污染@@”导致会影响到其他的走线@@,所以我们@@需要对地进行进一@@步的优化@@。虽然该板子已经有一@@个@@0Ω电阻接地@@,但是明显该接地点并不能起到降低地阻抗的效果@@。在研究了@@PCB后@@,我们需要增加@@几个接地点以优化模拟地@@阻抗和噪声回路@@。

(增加@@0Ω电阻位置优化接地阻抗@@)

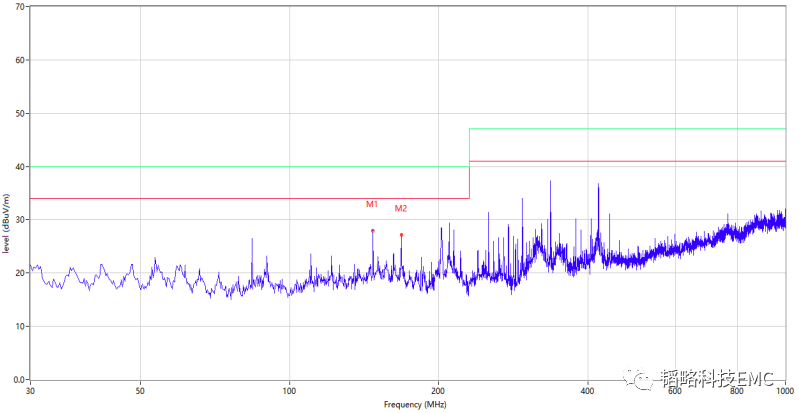

在优化接地后@@@@@@,具体数据如下@@图@@:

(优化接地后@@@@测试数据@@)

可以发现@@,优化接地后@@@@,时钟频点有很明显的下降@@,虽然我们在时钟源头整改没有效果@@,但是我们优化时钟接收端的地后@@却又明显的效果@@,说明该模块的地阻抗和系统地的阻抗存在阻抗差导致时钟回路改变从而导致时钟辐射超标@@@@,所以我们@@PCB设计的时候要注@@意尤其模拟地@@和系统地的接地情况@@,在保持分地的情况也要考虑回路和阻抗差@@,从而从设计避免后@@续不必要的改版时间和拖延产品上市时间@@。

四@@. 总结@@

时钟辐射超标@@问题确实是@@EMC整改过程@@非常棘手的问题@@,但是我们可以在设计初期就做好设计和预防@@,就可以尽量避免大部分的问题出现@@。

注@@:以上仅为本人观点@@,如有不足之处@@,敬请指教@@。