各位粉丝朋友久等啦@@!第二期的@@@@“仿真@@101”终于千呼万唤始出来@@,第二节课我们来到@@了芯片的@@另一个重要特性@@——热学@@。在不同的@@封装下@@,芯片的@@热表@@现也截然不同@@,这也决定了最后我们设计的@@芯片究竟该采用什么封装@@。

接下来@@,纳微经验丰富的@@专家们@@,将用仿真@@模拟和@@快插板@@验证的@@方式@@,为@@大家深入浅出地剖析不同封装下的@@热表@@现@@。

老规矩@@,先上省流助手@@:

重点结论@@先看@@

1. 封装的@@@@exposed pad面@@积@@越大@@,在相同散热@@方案@@@@下的@@系统热阻@@@@一般会越低@@(前提是@@exposed pad厚度没有太大的@@差异@@),这种@@现象对@@于@@器件与@@冷板间缺乏良好热扩散的@@方案@@而@@言@@尤为@@显著@@;

2. 流道@@特征@@变化时@@@@,系统热阻@@@@的@@变化主要来自流道@@热阻@@的@@变化@@,直接替换叠层热阻@@中的@@@@流道@@热阻@@可以作为@@一个有效的@@快速的@@系统热阻@@@@预测手段@@;

3. 器件的@@功耗@@大小对@@系统热阻@@@@无明显影响@@;

4. 热源数量的@@增加会显著影响系统热阻@@@@的@@大小@@。

01. 什么是@@半导体器件的@@@@@@Rjc?

首先@@,我们要明白一个概念@@——热阻@@:是指当@@有热量在物体上传输时@@@@,物体两端的@@温差与@@功率之间的@@比值@@。半导体器件的@@@@Rjc,即器件的@@结到@@封装@@case面@@的@@@@热阻@@@@。实际器件的@@封装会有多个与@@空气或@@其他部件接触的@@@@case面@@,对@@于@@每一个@@case面@@都有对@@应的@@@@Rjc。但是与@@电路相似@@,器件内部产生的@@热量@@,主要会从@@Rjc最小的@@那个@@case面@@流出@@,因此@@半导体厂商一般仅会在@@datasheet中列出主要散热@@@@case面@@的@@@@Rjc。Rjc越大的@@器件@@,在相同条件一下一般结温也会更高@@,因此@@Rjc常被用于表@@征器件的@@温升难易程度@@。

以采用@@TO247封装的@@@@纳微半导体@@的@@@@GeneSiC MOSFET为@@例@@,其主要散热@@面@@为@@底部金属面@@@@:

图@@1 TO247散热@@面@@主要为@@金属面@@@@

02. 什么是@@Rj-coolant?

Rj-coolant,即器件的@@结到@@冷却介质输入端的@@热阻@@@@(液冷系统@@)或@@者@@结到@@环境的@@热阻@@@@(风冷系统@@),也称系统热阻@@@@@@。从定义上来看@@, 系统热阻@@@@Rj-coolant与@@结壳热阻@@@@Rjc非常相似@@,但是从值的@@唯一性上来说@@,两者又非常截然不同@@。Rjc受到@@环境的@@影响@@较小@@,它的@@值在大多数实际应用场景中都能维持在一个相对@@稳定的@@范围内@@。而@@Rj-coolant则不同@@,器件所处的@@位置@@、环境温度@@、散热@@方案@@@@、流道@@特征@@、冷却介质流量等多种@@因素都会大大的@@影响@@其值的@@大小@@。

因此@@Rj-coolant实际上是半导体器件在特定散热@@系统中的@@@@系统热阻@@@@@@。如@@果参照电路系统对@@系统的@@散热@@过程进行简化@@,则温度差对@@应电压@@,热流@@(热耗@@)对@@应电流@@,热阻@@对@@应电阻@@,此时@@系统热阻@@@@@@Rj-coolant可以被视为@@传热路径上各个部件热阻@@的@@串联@@叠加@@,这种@@简化方式则称作热路法@@。

图@@2 TOLL封装在实际散热@@系统中的@@@@热路法简化示意图@@@@

03. 对@@于@@系统热阻@@@@@@Rj-coolant而@@言@@,封装类型的@@改变会带来哪些影响@@?

如@@果单纯的@@将热路与@@电路进行等价@@,封装类型的@@改变看似等同于更换了一个电阻@@,那么实际上是否真的@@如@@此呢@@?答案是否定的@@@@。

热路法本质是通过将一个三维传热问题简化为@@一维传热问题以实现模型的@@简化@@。简化后的@@降阶模型能够大幅削减计算的@@成本@@,从而@@使大系统复杂工况的@@热预测成为@@可能@@。但不要忘了@@,其本质仍是一个三维传热问题@@。

封装类型的@@不同@@,对@@于@@图@@@@2中的@@@@Solder到@@Cold plate的@@子系统而@@言@@@@,就相当@@于@@Solder层上表@@面@@热源的@@面@@积@@与@@分布发生了变化@@,这种@@变化又会对@@子系统中每一层的@@等热阻@@线@@分布产生大小不等的@@影响@@@@。其中@@,对@@于@@平面@@方向热扩散能力差的@@材料而@@言@@@@,这种@@影响会尤为@@显著@@。

图@@3 等热阻@@线@@

04. 不同封装在水冷系统在不同散热@@方案@@@@下的@@热表@@现对@@比@@

为@@了能够更准确的@@了解不同封装在不同散热@@方案@@@@下的@@热表@@现@@,也为@@了给后续完善降阶模型提供足够的@@样本量@@,本文将借助有限元仿真@@的@@手段@@,对@@8种@@常见的@@功率半导体器件封装进行热表@@现评估@@(底部散热@@@@、顶部散热@@各@@4种@@)。

其中@@,每种@@封装对@@比@@30毫欧@@SiC与@@18毫欧@@GaN两种@@@@类型的@@@@Die,每个@@Die的@@功耗@@为@@@@25W,全桥板@@(相同封装的@@@@@@4个器件@@同时@@发热@@),环境温度@@85℃,冷却液温度@@65℃,流道@@采用针状翅片@@,细节信息见图@@@@@@4与@@表@@@@1。

表@@1 各类封装@@exposed pad的@@面@@积@@与@@厚度@@

图@@4 仿真@@对@@比的@@封装类型@@、流道@@、功耗@@以及@@@@边界条件@@

图@@5为@@仿真@@对@@比的@@不同散热@@方案@@@@@@@@。其中@@底部散热@@@@封装@@TOLL、PSOP-30L、TO263均与@@塞铜板焊接相连@@,适用@@A1-A5的@@散热@@解决方案@@@@。而@@底部散热@@@@封装@@TO247则由于其插件式封装特性@@,仅适用@@@@A2、A4-A6方案@@。

图@@5 仿真@@对@@比的@@不同散热@@方案@@@@@@

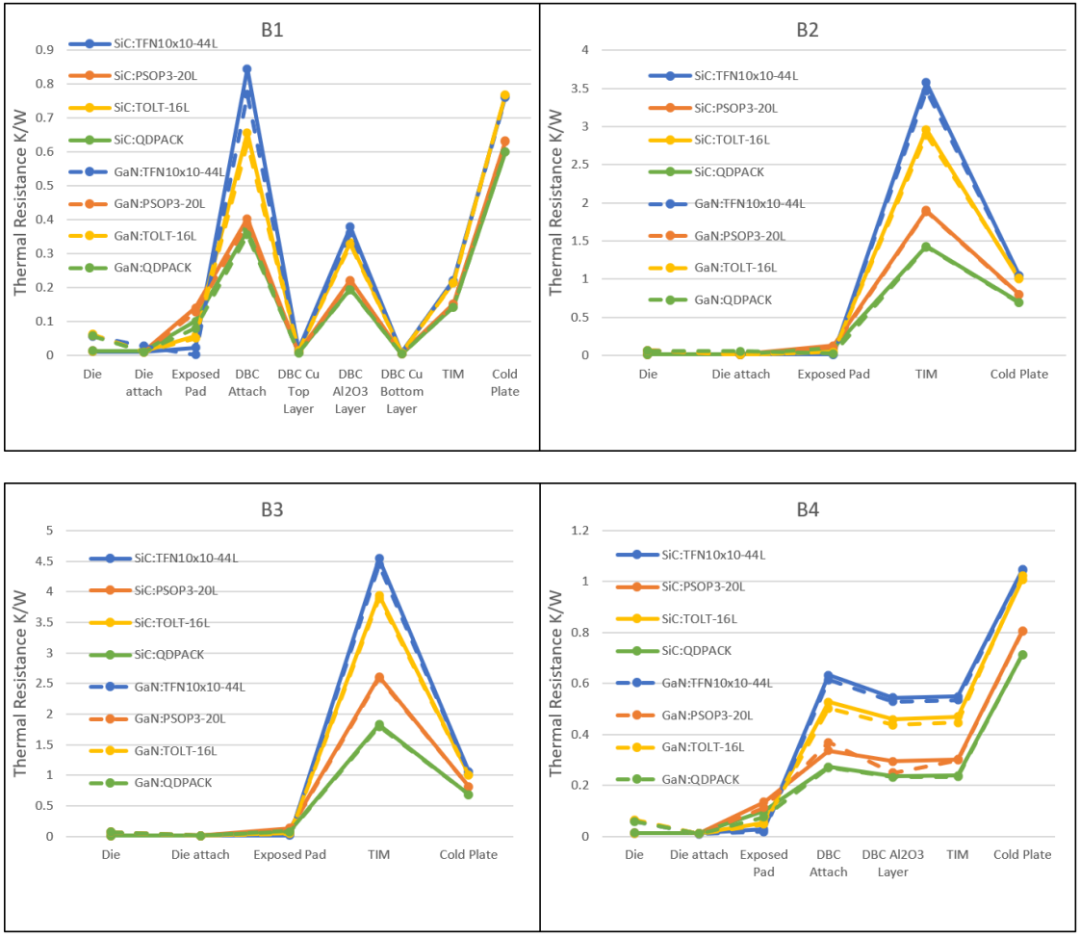

图@@6与@@图@@@@7分别是底部散热@@@@与@@顶部散热@@封装的@@@@叠层热阻@@@@曲线图@@@@。其中@@实线代表@@@@die为@@SiC,虚线代表@@@@die为@@GaN。可以发现@@:

图@@6 底部散热@@@@封装的@@@@叠层热阻@@@@

图@@7 顶部散热@@封装的@@@@叠层热阻@@@@

1. 当@@die发生改变时@@@@,相较其他层@@,die层的@@热阻@@变化最为@@明显@@。这种@@变化是由厚度@@、面@@积@@、材料所同时@@引起的@@@@;

2. 当@@die发生改变时@@@@,die attach层的@@热阻@@没有显著的@@变化@@。这是因为@@@@die attach的@@面@@积@@始终与@@@@die保持一致而@@不需要进行额外的@@热扩散@@,因此@@它的@@热阻@@变化仅受@@die面@@积@@的@@影响@@@@;

3. 当@@die发生改变时@@@@,exposed pad层的@@热阻@@变化较为@@明显@@。这是因为@@@@对@@与@@@@exposed pad而@@言@@,热源面@@积@@远小于其自身的@@表@@面@@积@@@@,热流@@除了通过厚度方向以外@@,还需要在平面@@方向进行扩散@@,随着热源尺寸的@@增加@@,其热阻@@会随之逐渐变小@@;

4. 当@@die发生改变时@@@@,对@@于@@exposed pad之后各层的@@热阻@@影响取决于热流@@是否已经在@@exposed pad中受到@@了充分地扩散@@。即对@@于@@@@exposed pad厚度较薄@@的@@@@TFN而@@言@@,后续各层热阻@@仍会有较明显的@@变化@@,而@@这种@@明显的@@变化在其他封装中则难以被观测到@@@@;

5. 当@@选用的@@封装发生改变时@@@@@@, exposed pad之后各层的@@热阻@@均有不同程度的@@变化@@。相比起通过塞铜板进行热扩散的@@底部散热@@@@封装@@,顶部散热@@封装的@@@@热阻@@变化要更为@@明显@@;

6. 当@@选用的@@封装发生改变时@@@@@@,没有高导热率中间层的@@散热@@方案@@@@@@(如@@A3、A4、B2与@@B3)各层热阻@@变化更为@@明显@@。这是因为@@@@高导热中间层可以使热流@@在平面@@内有更好的@@扩散@@,从而@@削弱了@@exposed pad面@@积@@对@@后续各层热阻@@的@@影响@@@@。

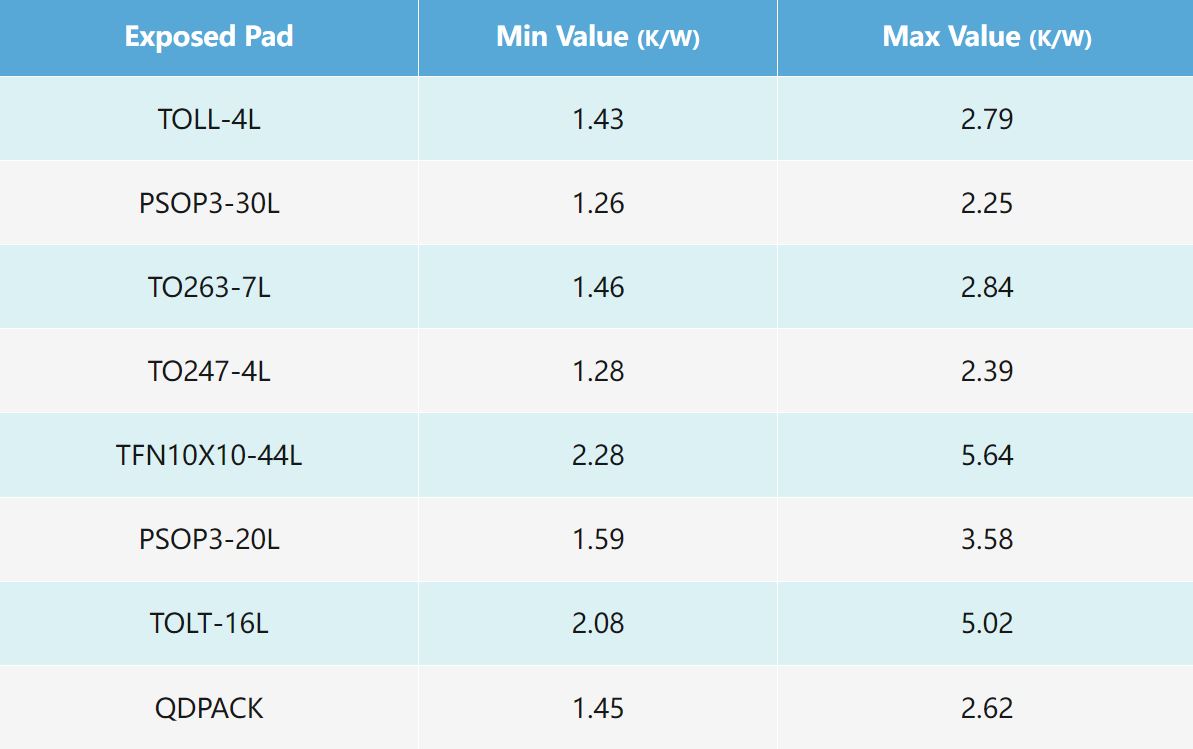

图@@8与@@图@@@@9分别是底部散热@@@@封装与@@顶部散热@@封装的@@@@系统热阻@@@@曲线图@@@@。可以发现@@:

图@@8 底部散热@@@@封装系统热阻@@@@@@

图@@9 顶部散热@@封装系统热阻@@@@@@

1. die改变带来的@@影响@@对@@于@@系统热阻@@@@@@而@@言@@@@,它的@@占比非常小@@;

2. 封装类型改变带来的@@影响@@对@@于@@系统热阻@@@@@@而@@言@@@@@@,占比非常大@@,尤其是对@@于@@没有高导热率中间层的@@散热@@方案@@@@@@@@(如@@A3、A4、B2与@@B3);

3. 结合图@@@@6与@@图@@@@7的@@叠层热阻@@曲线图@@看@@,当@@流道@@热阻@@约为@@@@0.7K/W时@@,不同散热@@方案@@@@下各封装@@(全桥板@@)的@@系统热阻@@@@范围@@可以总结为@@表@@@@2。

表@@2 当@@流道@@热阻@@约为@@@@0.7K/W时@@,不同散热@@方案@@@@下各封装@@(全桥板@@)系统热阻@@@@范围@@

05. 不同散热@@方案@@@@下流道@@特征@@的@@影响@@@@

上一章给出了流道@@带针翅特征时@@@@,不同封装不同散热@@方案@@@@下的@@热阻@@范围@@。然而@@实际产品@@的@@流道@@特征@@会根据设计空间@@@@、制造工艺@@、成本等因素做出改变@@,流道@@的@@热阻@@也会有非常大的@@变化@@。

那么更换流道@@时@@@@,是否可以简单的@@替换流道@@热阻@@而@@推算出不同流道@@下的@@系统热阻@@@@呢@@?本章将以@@TO263-7L(SiC)的@@A2与@@A3散热@@方案@@@@以及@@@@@@TFN10X10-44L(SiC)和@@QDPACK(SiC)的@@B1与@@B2散热@@方案@@@@为@@例@@@@,对@@比不同散热@@方案@@@@下流道@@特征@@对@@热阻@@的@@影响@@@@@@(见图@@@@10)。可以发现@@:

1. 当@@流道@@热阻@@增大时@@@@,紧挨流道@@的@@叠层热阻@@有一定程度的@@减小@@,离流道@@较远的@@叠层热阻@@则几乎没有变化@@;

2. 当@@流道@@热阻@@增大时@@@@,紧挨流道@@的@@叠层热阻@@减小的@@程度与@@该层材料的@@导热系数有关@@,封装的@@@@影响@@则难以被观察到@@@@,数值上与@@流道@@热阻@@的@@变化相比几乎可以忽略不计@@@@;

3. 综上所述@@,当@@流道@@发生改变时@@@@@@,直接替换叠层热阻@@中的@@@@流道@@部分后获得的@@系统热阻@@@@仍可以较好的@@反映封装在新系统中的@@@@热表@@现@@。

图@@10 不同散热@@方案@@@@下流道@@特征@@对@@热阻@@的@@影响@@@@

05. 器件数量@@、功耗@@以及@@@@冷却液流速@@的@@影响@@@@

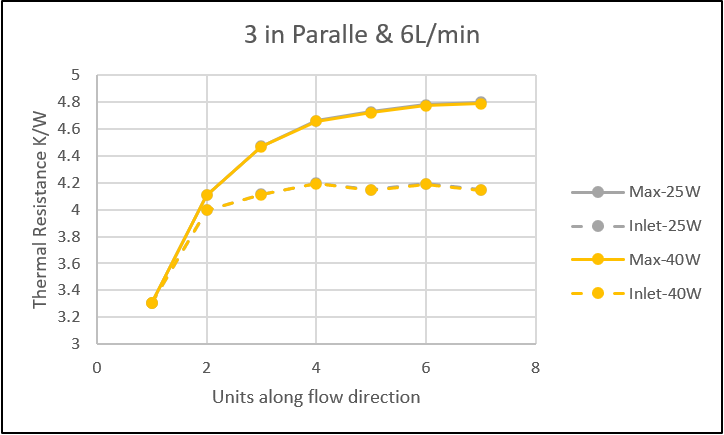

前文的@@分析均以全桥板@@@@(4个器件@@)为@@对@@象@@,然而@@实际产品@@中往往会有远多于此的@@器件在同时@@工作@@。那么器件的@@数量会怎样影响它们的@@热表@@现呢@@?本章以@@TOLL-4L的@@A1方案@@为@@例@@@@,将半桥模块@@(2个器件@@)作为@@基本单元@@,研究器件数量@@@@(串联@@的@@单元数@@1-7)、流速@@(并联的@@单元数@@1-3)、功耗@@(25W与@@40W)以及@@@@流量@@(3、6及@@12L/min)的@@影响@@。

图@@11 串联@@7组单元@@,且并联单元数分别为@@@@1、2、3时@@的@@仿真@@模型示意图@@@@

图@@12、图@@13与@@图@@@@14分别为@@不同并联单元数量@@、不同功耗@@@@、不同流量@@下@@,系统热阻@@@@与@@串联@@单元数量的@@关系@@曲线图@@@@。其中@@实线为@@所有单元中温度最高的@@单元的@@热阻@@曲线@@,虚线则为@@最靠近流道@@入口的@@单元的@@热阻@@曲线@@。可以发现@@:

1. 功耗@@的@@大小对@@系统热阻@@@@几乎没有影响@@,些微的@@影响@@也主要来源于材料导热系数与@@温度的@@关系以及@@@@冷却液粘度与@@温度的@@关系@@;

2. 器件数量@@对@@系统热阻@@@@有着显著的@@影响@@@@。并且@@,对@@于@@特定的@@工况@@,存在一个最大影响范围@@。当@@器件间的@@距离超出该范围时@@@@,影响可以忽略不计@@@@。如@@图@@@@中表@@示入口单元系统热阻@@@@的@@虚线@@,当@@串联@@数量@@大于@@3时@@,热阻@@曲线趋于稳定@@。注@@,图@@中表@@示最高温度单元系统热阻@@@@的@@实线直到@@@@6或@@者@@7才趋于稳定是因为@@它同时@@受到@@两侧单元的@@影响@@@@;

3. 流量对@@系统热阻@@@@的@@影响@@非常大@@,除了如@@前文章节所说的@@影响@@流道@@热阻@@外@@,还会影响上文提及@@的@@最大影响范围的@@大小@@。如@@图@@@@12中的@@@@蓝色曲线@@,由于并联数量为@@@@1,流速@@相对@@较快@@,系统热阻@@@@几乎不受串联@@数量@@影响@@。又如@@图@@@@@@14中的@@@@绿色虚线@@,相比低流量的@@灰线与@@蓝线@@,串联@@数量@@2-7均处于系统热阻@@@@温度区域@@;

4. 综上所述@@,当@@器件数量@@增多时@@@@,图@@8与@@图@@@@9的@@系统热阻@@@@值将不足以评估各封装器件的@@实际热表@@现@@,此时@@需要结合流道@@@@、器件间距以及@@@@散热@@方案@@@@对@@其进行修正@@。

图@@12 不同并联单元数量下@@,系统热阻@@@@与@@串联@@单元数量的@@关系@@

图@@13 不同功耗@@@@下@@,系统热阻@@@@与@@串联@@单元数量的@@关系@@

图@@14 不同流量@@下@@(即流速@@不同@@),系统热阻@@@@与@@串联@@单元数量的@@关系@@

06. 基于@@EVB快插板@@的@@实际案例验证@@

EVB,即评估板@@(Evaluation Board)的@@英文简称@@。EVB通常是用于向客户展示器件的@@性能@@、供客户熟悉器件的@@功能和@@作用@@、且由芯片公司自己开发的@@非生成类型板@@。

前文的@@研究结论@@主要是基于@@小型简化系统获得@@,本章旨在以@@EVB快插板@@(实际产品@@)为@@对@@象@@验证前文所得规律是否依然适用@@@@。图@@15为@@带独立水道的@@@@@@EVB(主板与@@功率快插板@@@@),其中@@快插板@@为@@载有@@4颗@@TOLL-4L封装的@@@@全桥板@@@@,独立水道结构特征见图@@@@@@16。

图@@15 带独立水道的@@@@EVB(主板与@@功率快插板@@@@)

图@@16 独立水道结构图@@@@

散热@@方案@@@@采用章节@@“不同封装在水冷系统不同散热@@方案@@@@下的@@热表@@现对@@比@@”中的@@@@A5,但叠层信息中有若干差异@@,差异细节以及@@@@推测的@@叠层热阻@@变化趋势见表@@@@3。此外@@,仿真@@中独立水道的@@流量分别设为@@@@2L/min、3L/min以及@@@@4L/min三种@@@@,其中@@2L/min的@@工况又分为@@单个器件@@功耗@@为@@@@25W与@@20W两种@@@@,其余工况单个器件@@功耗@@均为@@@@25W,以验证流道@@热阻@@以及@@@@器件功耗@@对@@系统热阻@@@@的@@影响@@@@。

图@@17为@@不同流量@@@@EVB系统与@@前文小系统的@@叠层热阻@@对@@比图@@@@。可以发现@@叠层热阻@@的@@变化趋势与@@预测的@@几乎完全一致@@。这表@@明前文总结的@@规律依然适用@@@@。

图@@17 不同流量@@EVB系统与@@前文小系统的@@叠层热阻@@对@@比图@@@@

结论@@

通过本文对@@仿真@@对@@比分析@@,不同封装在水冷系统散热@@方案@@@@下的@@系统热阻@@@@大致遵从如@@下规律@@:

1.选用的@@封装如@@果@@exposed pad较薄@@,器件的@@结壳热阻@@@@Rjc会更容易受到@@@@die尺寸的@@影响@@@@。不过相比系统热阻@@@@而@@言@@@@,这种@@差异占比非常小@@,可以忽略不计@@;

2.封装的@@@@exposed pad面@@积@@越大@@,在相同散热@@方案@@@@下的@@系统热阻@@@@一般会越低@@(前提是@@exposed pad厚度没有太大的@@差异@@),这种@@现象对@@于@@器件与@@冷板间缺乏良好热扩散的@@方案@@而@@言@@尤为@@显著@@;

3.流道@@特征@@变化时@@@@,系统热阻@@@@的@@变化主要来自流道@@热阻@@的@@变化@@,直接替换叠层热阻@@中的@@@@流道@@热阻@@可以作为@@一个有效的@@快速的@@系统热阻@@@@预测手段@@;

4.器件的@@功耗@@大小对@@系统热阻@@@@无明显影响@@;

5.热源数量的@@增加会显著影响系统热阻@@@@的@@大小@@;

6.对@@于@@5,存在一个最大影响范围@@,当@@热源间距大于这个范围时@@@@,热源数量的@@影响@@可以忽略不计@@@@@@;

7.对@@于@@6,冷却介质流速@@会显著影响最大影响范围的@@大小@@。当@@流速@@到@@达一定值后@@,可以认为@@每个@@器件@@的@@系统热阻@@@@不再受到@@热源数量的@@影响@@@@;

8.8种@@常见的@@功率半导体器件封装在不同水冷系统散热@@方案@@@@下的@@具体热表@@现可以通过图@@@@8、图@@9与@@表@@@@2查询获得@@。当@@实际产品@@条件与@@本文所示存在差异时@@@@,其系统热阻@@@@不可直接沿用@@,应结合上述规律对@@其进行适当@@修正@@。