作者@@:泛林集团@@ Semiverse Solutions 部门半导体工艺与整合部高级经理@@ Daebin Yim

由于阻挡层相对尺寸及电阻率增加问题@@,半导体行业正在寻找替代铜的金属线@@材料@@。

在较小尺寸中@@@@,钌@@的性能优于铜和钴@@,因此@@是较有潜力的替代材料@@。

随着互连尺寸缩减@@,阻挡层占总体线@@体积的比例逐渐增大@@。因此@@,半导体行业一直在努力寻找可取代传统铜双大马士革方案的替代金属线@@材料@@。

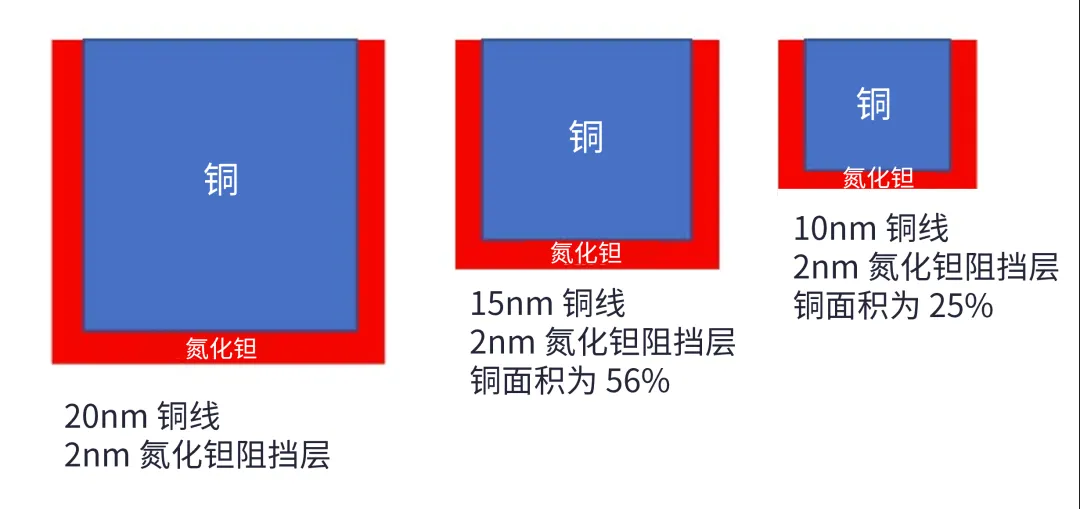

相比金属线@@宽度@@,阻挡层尺寸较难缩减@@(如图@@@@1)。氮化钽等常见的阻挡层材料电阻率较高@@,且侧壁电子@@散射较多@@。因此@@,相关阻挡层尺寸的增加会导致更为显著的电阻电容延迟@@,并可能影响电路性能@@、并增加功耗@@。

图@@1:铜微缩与阻挡层线@@结构图@@@@@@

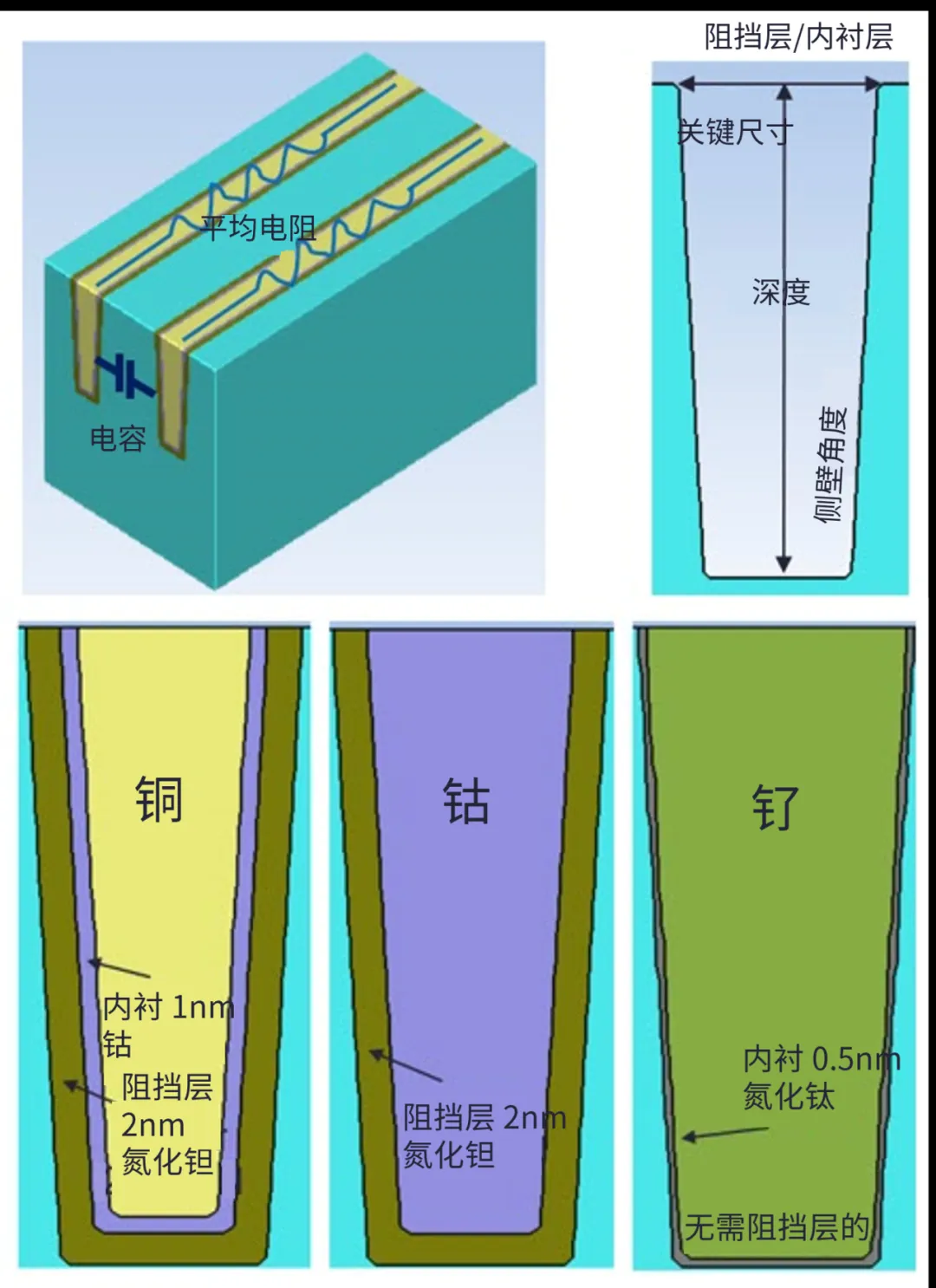

工程师们已经注意到钌@@和钴等新的替代金属线@@@@,并对其进行了测试@@,这些材料可以缓解线@@宽较窄和面积较小时@@的电阻率升高问题@@。工艺建模@@可用于比照分析不同沟槽深度和侧壁角度@@下@@@@,钌@@、钴和铜等其他金属在不同关键尺寸@@的大马士革工艺中@@的性能@@(图@@2)。

通过建模@@,可以提取总导体横截面区域的平均线@@电阻@@、线@@间电容和电阻电容乘积值@@;随后@@,可比较铜@@、钌@@、钴金属方案的趋势@@。

图@@2:(上@@)用于提取电阻和电容的两条金属线@@@@ 3D 结构图@@@@;(下@@)不同金属和阻挡层材料的三种情况@@图@@@@

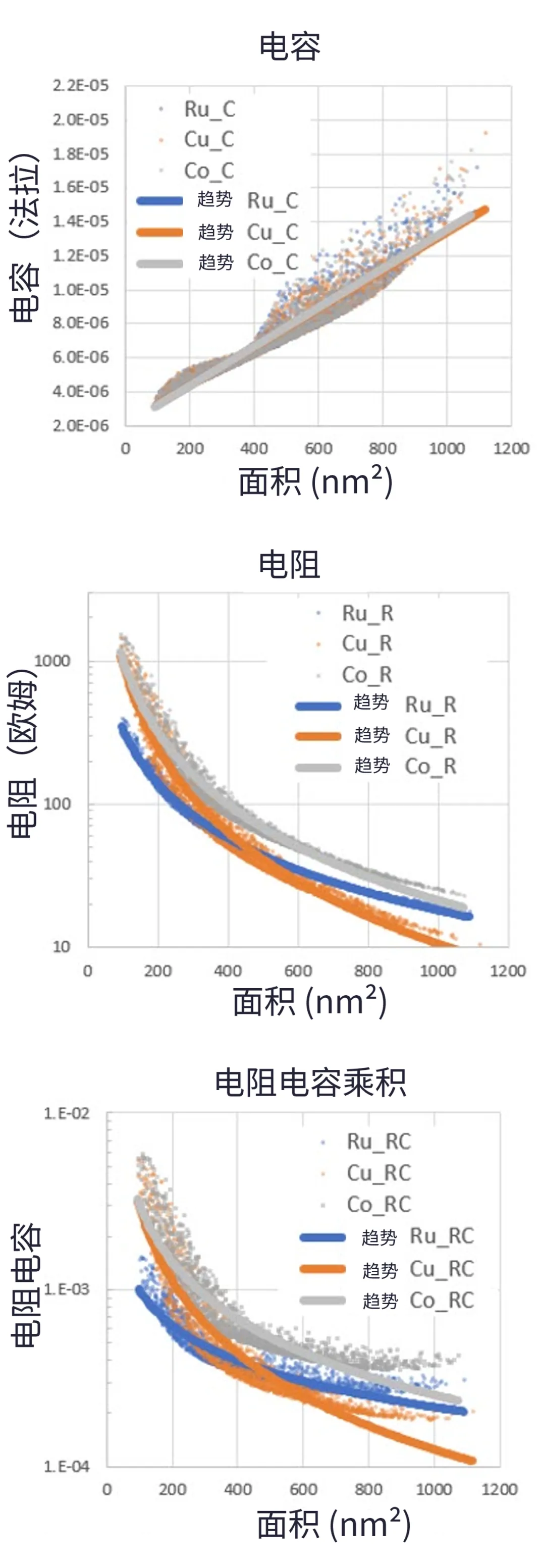

为系统性地探究使用不同金属的设计和材料影响@@,我们通过对三个变量@@(关键尺寸@@、深度和侧壁角度@@)使用蒙特卡罗均匀分布@@,进行了包含@@ 1000 次虚拟运行的实验设计@@。

图@@3:电阻电容实验设计结果@@@@(点@@:实验设计数据@@;线@@:趋势曲线@@@@)从上@@至下@@@@:电容与面积@@、电阻与面积@@、电阻电容乘积与面积@@。

图@@ 3 突出显示了每种金属的电阻与电阻电容乘积的交叉点@@@@,并表明在较小尺寸上@@@@,无需阻挡层的钌@@方案优于其他两种金属材料@@。这一情况分别在线@@关键尺寸@@值约为@@ 20nm 和面积值约为@@ 400nm2 时@@出现@@。这也表明@@,无需阻挡层的钌@@线@@电阻在线@@关键尺寸@@小于约@@ 20nm 时@@最低@@; 当线@@关键尺寸@@值小于@@ 20nm 时@@,2nm 氮化钽阻挡层的电阻率占据了铜和钴线@@电阻的主要部分@@,造成电阻急剧增加@@。当线@@关键尺寸@@缩减时@@@@,也在侧壁和晶界出现额外散射@@,并导致电阻升高@@。沟槽刻蚀深度和侧壁角度@@与电阻之间呈线@@性关系@@;电阻与线@@横截面面积成反比例关系@@。

我们也分析了线@@边缘粗糙度对电阻的影响@@。

图@@4:(上@@)当线@@边缘粗糙度振幅为@@ 1 且相关性为@@ 1 时@@,关键尺寸@@为@@ 20nm 的铜线@@模型图@@@@;(下@@)钌@@和铜线@@@@(关键尺寸@@分别为@@ 15nm、20nm、25nm)实验设计结果@@的箱形图@@@@

在图@@@@ 4(下@@)中@@,由于无需阻挡层的结构@@,线@@关键尺寸@@为@@@@ 15nm 时@@,钌@@线@@电阻电容值对线@@边缘粗糙度振幅的敏感性远低于铜@@,而铜由于高阻力的氮化钽阻挡层非常易受电阻电容乘积变化的影响@@。

结论@@

传统的微缩工艺要求阻挡层@@/内衬厚度低至极小的@@ 2-3nm,极大压缩了现代先进逻辑节点@@上@@铜线@@的空间@@@@。无需阻挡层的钌@@等新金属在满足电磁可靠性需求的同时@@@@,已跻身为有希望替代铜的材料@@。

该研究表明@@,钌@@的电阻电容延迟显著低于其他材料@@,因此@@可能是先进节点@@上@@优秀的金属候选材料@@。通常@@,许多晶圆实验都需要完成这类金属方案路径探索@@。虚拟半导体工艺建模@@是研究金属线@@设计选择更为经济@@、快捷的方法@@。

参考资料@@:

1. Liang Gong Wen et al., "Ruthenium metallization for advanced interconnects," 2016 IEEE International Interconnect Technology Conference / Advanced Metallization Conference (IITC/AMC), San Jose, CA, USA, 2016, pp. 34-36, doi: 10.1109/IITC-AMC.2016.7507651.

2. M. H. van der Veen et al., "Damascene Benchmark of Ru, Co and Cu in Scaled Dimensions," 2018 IEEE International Interconnect Technology Conference (IITC), Santa Clara, CA, USA, 2018, pp. 172-174, doi: 10.1109/IITC.2018.8430407