本文转载自@@: TechInsights微信公众号@@

2021年@@10月@@12日@@,三星@@宣布@@“三星@@新的五层@@@@EUV工艺@@实现了业界最高的@@DRAM位密度@@,将生产率提高@@了约@@20%”[1]。TechInsights在@@2023年@@2月@@17日@@发布的三星@@@@Galaxy S23 plus智能手机中获得了三星@@@@D1a LPDDR5X DRAM器件@@[2]。经过深入的@@SEM和@@TEM成像@@,并结合@@TEM EDS/EELS元素分析@@,TechInsights即将发布三星@@@@D1a nm 16 Gb LPDDR5X器件@@的@@分析报告@@。基于结构和@@材料逆向工程分析数据@@,TechInsights发现了四种@@EUV光刻@@(EUVL)工艺@@,用于阵列@@有源切割@@/外围有源@@(有源修剪@@)、位线接触@@(BLC)、存储节点接触垫@@(SNLP)/外围第一金属层@@@@ (M1)和@@存储节点@@(SN)管图@@形化@@@@。通过逆向工程分析没有明显的证据来确定@@EUVL工艺@@的第五层@@图@@形化@@层@@@@。

下表列出了三星@@@@D1y nm、D1z nm和@@D1a nm工艺@@器件@@的@@阵列@@有源切割@@、BLC、SNLP、SN管的最小宽度和@@节距@@,以及用于每层@@制模的光刻@@工艺@@@@@@。

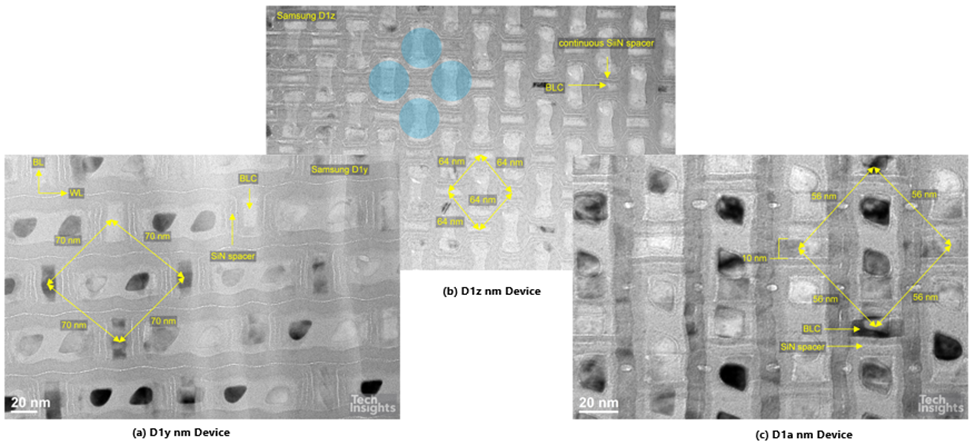

下图@@包含了三星@@@@D1a nm(图@@a)、D1z nm(图@@b)和@@D1y nm(图@@c)器件@@在@@存储阵列@@有源层@@的@@@@TEM平面视图@@@@。存储器阵列@@中的有源切口具有交错孔布局@@。三星@@D1y nm器件@@的@@阵列@@有源切割间距为@@@@68 nm,达到了@@193i光刻@@的分辨率极限@@。单@@193i光刻@@工艺@@@@用于图@@形化@@阵列@@有源切割@@/外围有源@@。三星@@D1z nm器件@@的@@阵列@@有源切割间距为@@@@63 nm。双图@@形化@@工艺@@可能用于图@@形阵列@@有源切割@@/外围有源@@。三星@@D1a nm器件@@的@@阵列@@有源切割间距为@@@@56 nm。

图@@1:在@@DRAM阵列@@有源层@@上的@@TEM平面视图@@@@

图@@2是三星@@@@D1a nm (a)、D1z nm (b)和@@D1z nm (c)器件@@在@@外围有源@@层@@@@的@@SEM平面视图@@@@图@@像@@。WL有源驱动中间的@@T型@@STI有一个尖角@@,如图@@@@2(a)所示@@;而@@WL有源驱动中间的@@T型@@STI有一个相对光滑的角@@,如图@@@@2(b)和@@图@@@@2(c)所示@@。这清楚地表明@@,存储阵列@@中的有源切口和@@外围@@的有源切口采用的是单@@一@@@@EUVL工艺@@,而@@不是@@193i双重图@@形化@@工艺@@@@。

图@@2:外围有源@@层@@@@SEM平面图@@@@

图@@3为三星@@@@D1y nm (a)、D1z nm (b)和@@D1a nm (c)在@@DRAM位线接触@@(BLC)层@@的@@TEM平面视图@@@@图@@像@@。BLC具有如下图@@所示@@的交错孔布局@@。三星@@D1y nm器件@@的@@BLC间距为@@70 nm(图@@a),这是@@193i光刻@@的分辨率极限@@。因此@@,采用单@@一@@的@@193i光刻@@工艺@@@@对@@BLC进行图@@形化@@@@。如图@@@@3 (b)所示@@,三星@@D1z nm器件@@的@@BLC间距为@@64 nm;由于在@@@@BLC特殊区域@@(如蓝点所示@@@@)使用掩膜的负色调显影@@(NTD)光刻@@工艺@@@@来对@@BLC进行图@@形化@@@@设计@@,因此@@可以观察到连续的@@SiN间隔@@(参见有关三星@@@@12 Gb 1z EUV LPDDR5 Advanced Memory Essentials, AME2102 -801的更多详细信息@@)。如图@@@@3(c)所示@@,三星@@D1a nm器件@@的@@BLC间距为@@56 nm;如图@@@@3 (a)所示@@,BLC SiN间隔@@片不是连续的@@,这与三星@@@@@@D1y nm器件@@中@@的@@BLC SiN间隔@@片相同@@。单@@个@@EUVL工艺@@可能用于三星@@@@D1a nm器件@@中@@的@@BLC图@@形化@@。

图@@3:阵列@@BLC层@@TEM平面视图@@@@

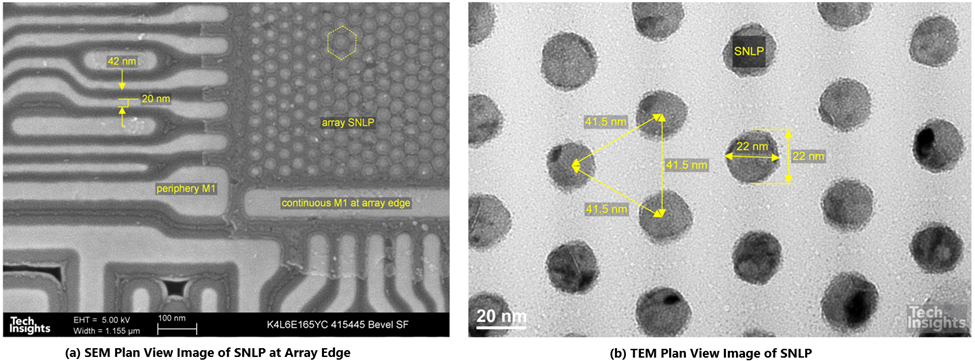

图@@4包括了三星@@@@D1a nm器件@@SNLP层@@的@@SEM (a)和@@TEM (b)平面视图@@@@图@@像@@。与三星@@@@D1z nm制程器件@@相同@@,圆形@@SNLP和@@阵列@@边缘的连续@@M1线表明使用单@@个@@@@EUVL制程对存储节点接触垫@@@@(SNLP)和@@外围@@M1进行了图@@形化@@@@。

图@@4:三星@@D1a nm器件@@阵列@@@@SNPL层@@的@@SEM和@@TEM平面视图@@@@

图@@5为三星@@@@D1z nm (a)和@@D1a nm (b)器件@@电容层@@的@@@@TEM平面视图@@@@图@@像@@。D1z nm器件@@的@@电容存储节点@@(SN)管间距为@@@@46.0 nm, D1a nm器件@@的@@SN管间距为@@@@41.5 nm。在@@三星@@@@D1z器件@@中@@,采用双向自对准双图@@像化工艺@@对@@SN管进行图@@像化@@(详见三星@@@@12Gb 1z EUV LPDDR5 process Flow Full, PFF-2102-801)。如图@@@@5 (a)所示@@,由于双向自对准图@@像化工艺@@的偏移和@@工艺@@均匀性问题@@,部分@@SN管在@@@@一个方向上比另一个方向略微拉长@@。D1a nm器件@@中@@的@@SN管在@@@@TEM斜角水平呈圆形@@@@,直径为@@23 nm(图@@5 (b))。因此@@,单@@一@@EUVL工艺@@可能用于三星@@@@D1a nm器件@@的@@SN管图@@案@@。

图@@5:在@@阵列@@电容层@@的@@@@TEM平面视图@@@@

References:

[1] Samsung Starts Mass Production of Most Advanced 14nm EUV DDR5 DRAM: https://news.samsung.com/global/samsung-starts-mass-production-of-most-a...

[2] Samsung Announces Global Launch of the Galaxy S23 Series: https://news.samsung.com/global/samsung-announces-global-launch-of-the-g...