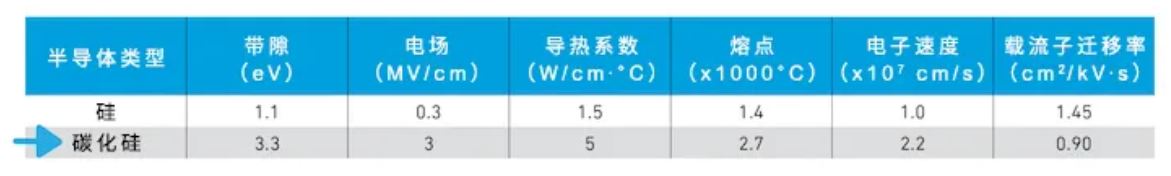

在之前一篇题为@@《功率电子@@器件@@从硅@@(Si)到碳化硅@@(SiC)的@@过渡@@》的@@博文中@@@@,我们探讨了碳化硅@@(SiC)如何成为功率电子@@市场一项@@“颠覆行业生态@@”的@@技术@@@@。如图@@@@1所示@@,与@@硅@@(Si)材料相比@@@@,SiC具有诸多技术@@优势@@,因此我们不难理解为何它已成为电动汽车@@(EV)、数据中@@心和@@太阳能@@/可再生能源等许多应用领域中@@备@@受青睐的@@首选技术@@@@。

图@@1.硅与@@碳化硅的@@对比@@

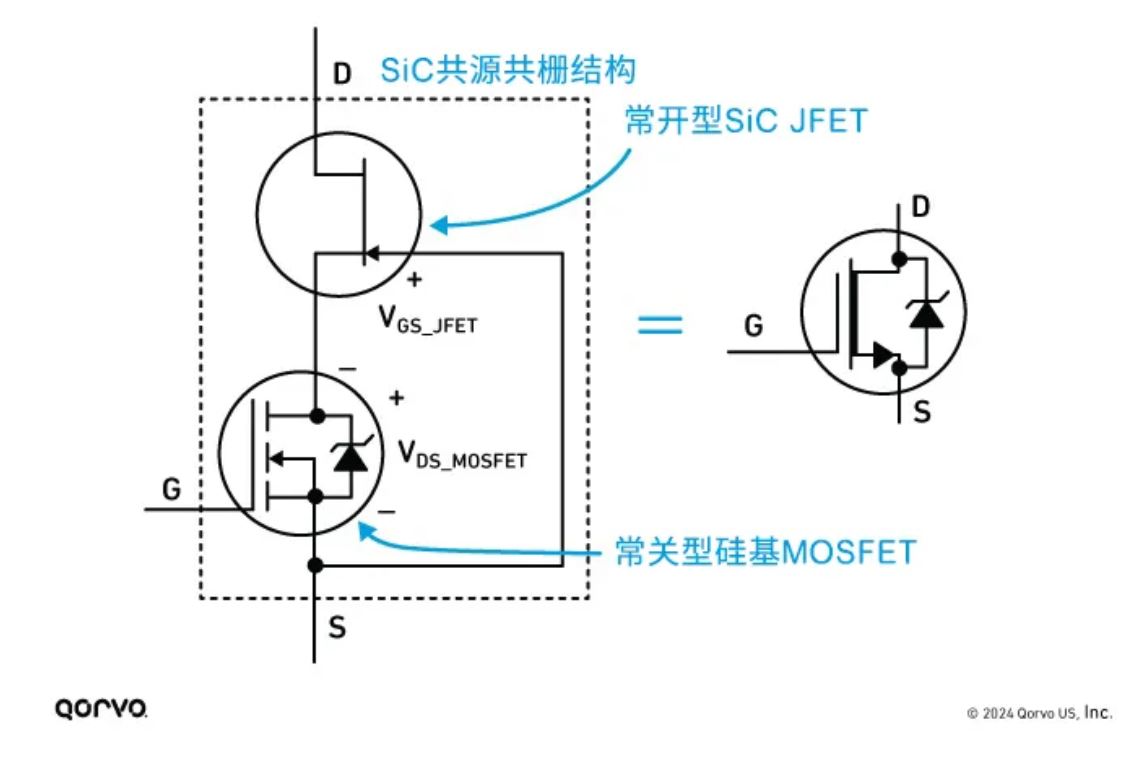

众多终端产品制造商纷纷选择采用@@@@SiC技术@@替代硅基@@工艺@@,来开发基于双极结型晶体管@@(BJT)、结栅场效应晶体管@@(JFET)、金属氧化物@@半导体场效应晶体管@@(MOSFET)和@@绝缘栅双极晶体管@@(IGBT)的@@电源产品@@。然而@@,Qorvo研发的@@@@SiC“共源共栅结构@@@@”FET器件@@(如图@@@@2所示@@)使这项技术@@更进一步@@。这些器件@@基于独特的@@@@“共源共栅结构@@@@”电路配置@@,将一个常开型@@SiC JFET器件@@与@@一个硅基@@@@MOSFET共同封装@@,形成一个集成的@@常关型@@SiC FET器件@@。在接下来的@@段落中@@@@,我们将详细阐述@@ Qorvo 研发的@@@@ SiC FET(共源共栅结构@@@@FET)相较于同类@@SiC MOSFET的@@显著优势@@。

图@@2.Qorvo SiC FET(“共源共栅结构@@@@”FET)器件@@结构@@框图@@@@

SiC MOSFET或@@SiC FET与@@硅@@基@@器件@@相比@@@@拥有几个显著优势@@。首先@@,SiC作为一种宽带隙材料@@,具有更高的@@击穿电压@@,因而可以使用更薄的@@器件@@来支持更高的@@电压@@。除此之外@@,SiC相较于硅基@@器件@@还有以下优势@@:

对于给定的@@电压和@@电阻等级@@,SiC可以实现更高的@@工作频率@@,因此可以减少无源器件@@的@@体积@@,从而减小整个系统的@@尺寸@@及成本@@

对于更高的@@电压等级@@(1200V或@@更高@@),SiC能够以较低的@@功率损耗实现高频开关@@;而在如此电压等级下仍能胜任的@@硅基@@器件@@实际上几乎不存在@@

在任何给定的@@封装中@@@@,SiC相对硅基@@产品具有更低的@@导通电阻和@@开关损耗@@

在与@@硅@@器件@@相同的@@设计中@@@@,SiC能够让客户获得更高的@@效率@@、更出色的@@散热性能@@,和@@更高的@@系统额定功率@@

这些优势同样体现在@@Qorvo SiC FET的@@性能上@@。作为一种更新且功能更强大的@@器件@@@@,Qorvo SiC FET针对多种功率应用进行了优化@@,并带来了以下额外收益@@:

Qorvo SiC FET的@@架构采用@@标准硅栅极驱动器@@,这使得从硅到@@SiC的@@过渡@@更加顺畅@@,同时也为设计师提供了更大灵活性@@

在给定封装中@@@@,具有行业最低的@@漏@@-源导通电阻@@ RDS(ON),可最大程度提升系统效率@@

更低的@@电容允许更快的@@开关速度@@,进而实现更高的@@工作频率@@;这进一步减小了电感器和@@电容器等大体积无源@@188足彩外围@@app 的@@尺寸@@

与@@硅@@基@@IGBT相比@@,SiC FET在更高电压等级@@(1200V或@@更高@@)能够实现更高的@@工作频率@@。硅基@@IGBT虽然传统上服务于这一细分市场@@,但通常速度较慢@@,仅在较低频率下使用@@,因此开关损耗较高@@

Qorvo SiC FET器件@@能在给定@@RDS(ON)的@@条件下@@获得更小的@@裸片尺寸@@,并减轻@@SiC MOSFET产品常见的@@栅极氧化物可靠性问题@@

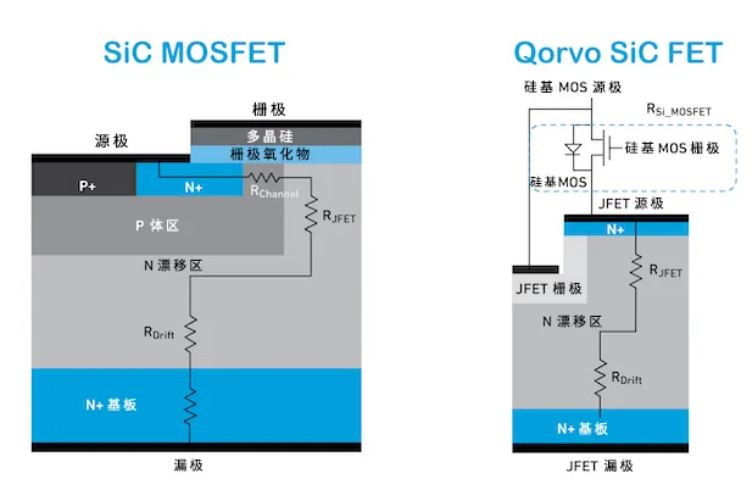

让我们花一些时间更深入地了解@@SiC MOSFET与@@Qorvo SiC FET两种功率技术@@间的@@差异@@。从下面的@@图@@@@3中@@,我们会发现@@SiC MOSFET技术@@不同于@@Qorvo的@@集成@@SiC FET——这是精心设计的@@结果@@。Qorvo利用@@SiC JFET消除了@@SiC MOSFET的@@栅极氧化层@@,进而消除了@@沟道电阻@@,让裸片尺寸更为紧凑@@。

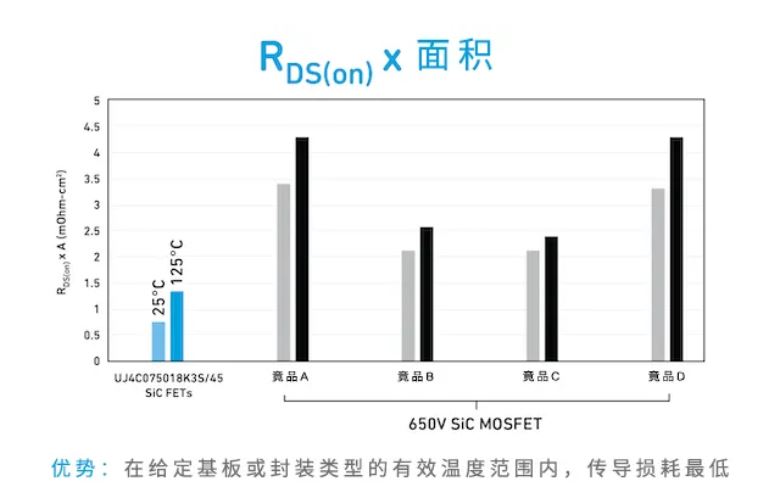

Qorvo SiC JFET较小的@@裸片尺寸成为其差异化优势的@@一个关键所在@@,并通过图@@@@4所示@@的@@@@‘RDS(ON) x A’(RdsA)品质因数@@(FOM)得到最佳体现@@。这意味着@@对于给定的@@芯片尺寸@@,Qorvo SiC FET提供了更低的@@导通电阻额定值@@;换言之@@,在相同的@@@@RDS(ON)条件下@@,Qorvo SiC FET所需的@@@@SiC裸片尺寸更小@@。Qorvo凭借在@@RdsA FOM方面的@@卓越表现树立了行业领先地位@@;其所提供的@@超低额定电阻产品能适用@@TOLL和@@D2PAK等相对较小的@@行业标准封装@@,让这一点得以充分展现@@。

图@@3.SiC MOSFET与@@Qorvo SiC FET的@@比较@@

Qorvo的@@SiC FET与@@SiC MOSFET相比@@具有更低的@@输出电容@@Coss。输出电容较低的@@器件@@在低负载电流下开关速度更快@@,电容充电延迟时间更短@@。这意味着@@,由于减少了对电感器和@@电容器等较大体积无源@@188足彩外围@@app 的@@需求@@,使得终端设备@@能够实现更小的@@体积@@、更轻的@@重量@@、更低的@@成本@@,并获得更高的@@功率密度@@。

图@@4.Qorvo SiC FET与@@SiC MOSFET竞品对比@@

SiC MOSFET还面临以下技术@@挑战@@:

SiC MOS沟道电阻高@@,导致电子@@迁移率较低@@

在栅极偏压较高的@@情况下@@,Vth可能发生漂移@@;这限制了栅极到源极的@@电压驱动范围@@

体二极管具有较高的@@拐点电压@@,因此需要同步整流@@

然而@@,采用@@Qorvo SiC FET后@@,上述缺陷得以根本解决@@,原因如下@@:

SiC JFET 结构@@的@@器件@@上摒弃了@@MOS(金属氧化物@@)结构@@,因此器件@@更加可靠@@

相同芯片面积下@@,漏极至源极电阻更低@@

电容更低@@,相当于更快的@@开关转换和@@更高的@@频率@@

尽管市场上可供选择的@@@@SiC功率半导体种类繁多@@,但在某些特定应用中@@@@,一些器件@@的@@表现确实比其它器件@@更为出色@@。Qorvo的@@集成@@SiC“共源共栅结构@@@@”FET技术@@便是其中@@的@@佼佼者@@;其凭借低@@RDS(ON)、低输出电容@@,和@@高可靠性等独特优势提供了卓越性能@@。这些品质因数@@推动@@Qorvo的@@SiC FET技术@@在其它技术@@无法企及的@@领域大放异彩@@。此外@@,SiC FET的@@附加性能使其在@@AC/DC电源单元@@、DC/DC储能和@@可再生能源应用@@,以及电动汽车快速充电器中@@实现更高的@@效率@@。

文章来源@@:Qorvo Power